참고: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second Edition

Chapter 9 - Operational Amplifiers (pg. 374~390)

9. Operational Amplifiers

9.7. Common-Mode Feedback

CMFB 개요

CMFB는 common-mode feedback의 줄임말로, differential circuit에서 필요합니다.

Fully differential circuit은 single-ended 구조보다 output swing이 크고, mirror pole이 없어서 closed-loop speed가 빠른 등의 장점이 있는데, 대신 gain이 큰 경우에는 CMFB를 걸어줘야 합니다.

Fig. 9.40은 simple differential pair와, 여기에 input과 output을 short시켜서 differential negative feedback을 만든 회로입니다.

두 회로 다 input, ouptut common-mode level이 Vdd-IssRd/2임을 특별한 계산 없이 알 수 있습니다.

이렇게 한눈에 output CM level을 알 수 있는 회로가 잘 define된 회로입니다.

그런데 high-gain differential pair같은 경우에는 그렇지 않습니다.

(Fig. 9.41(a)) 직전 회로에서 load resistor를 PMOS current source(M3, M4)로 바꾼 형태인데요.

이 회로에서는 M3, M4에 흐르는 전류 Ip와 M1, M2에 흐르는 In이 서로 균형을 이뤄야 모든 transistor가 saturation에서 동작할 수 있습니다.

(Fig. 9.41(b)) 그런데 PMOS(Id3,4=Ip), NMOS(Iss=In) current mirror의 mismatch 때문에 Ip-In의 error가 발생하게 되고, 이로 인해 output voltage 변화가 (Ip-In)(Rp||Rn)만큼 발생하게 됩니다.

이때 high-gain differential pair에서는 output node에서의 (Rp||Rn)이 꽤 큰 값이라, voltage error도 꽤 커서 p 또는 n-type current source들을 triode region으로 밀어낼 수 있습니다.

이렇게 high-gain differential pair에서 두 current source의 전류값 간에 차이가 발생하면, output common-mode level이 심각하게 흔들리게 됩니다.

이런 mismatch는 모든 회로에서 발생하는데, differential feedback으로는 이걸 바로잡을 수 없고, CMFB를 사용해서 op amp를 정상동작시켜야 합니다.

그래서 이걸 잡아주기 위해 CMFB를 걸어줍니다.

CMFB는 세 단계로 진행됩니다.

- Output CM level을 sensing하는 단계

- 이를 reference와 비교하는 단계

- 둘 간의 error를 amp의 bias network로 다시 보내는 단계

CM Sensing 방법

먼저 common-mode를 sensing하는 부분입니다.

Fig. 9.45는 resistive divider로 Vout을 sensing하는 common-mode feedback입니다.

이때 Vout,cm은 이와 같고, R1=R2일 때 Vout,cm=(Vout1+Vout2)/2가 됩니다.

Open-loop gain이 떨어지지 않게 하려면 R1과 R2가 op amp의 output impedance보다 훨씬 커야 합니다.

그런데 큰 resistor를 쓰면 공간을 많이 차지하고, parasitic capacitance가 크다는 문제가 있습니다.

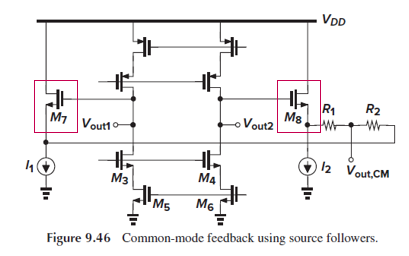

그래서 resistive loading을 없애기 위해, 양 output과 resistor 사이에 source follower M7과 M8을 넣었습니다.

그런데 이 경우에는 Vout1, Vout2의 swing이 클 때 M7, M8이 saturation을 유지할 수 있도록 I1, I2, R1, R2를 충분히 크게 설정해 줘야 합니다.

이게 무슨 말이냐면~

Vout2가 Vout1보다 훨씬 큰 경우에, 남는 전류 Ix가 I1 쪽으로 흐르기 때문에, I1이 Ix와 Id7를 둘다 받을 수 있을 정도로 (‘sink’할 수 있도록) 충분히 큰 값이거나, R1+R2가 충분히 커서 Ix를 작게 만들어야 합니다.

그러지 않으면, Id7=0이 되어버려서 Vout,CM이 더이상 의도한 대로 나오지 않게 됩니다.

<Fig. 9.46>

그런데 Fig. 9.46은 differential output swing을 제한한다는 단점이 있습니다.

CMFB가 없다면, Fig. 9.46 회로의 Vout의 가능한 최솟값은 Vod3+Vod5입니다.

CMFB가 있는 상태에서는 Vout의 최솟값이 Vgs7+Vi1으로, Vgs7이 overdrive voltage+threshold voltage, Vi1이 overdrive voltage라 치면, 이는 Vod 2개+Vth 1개입니다.

Fig. 9.46처럼 source follower를 이용한 sensing 방법을 사용하면 output swing이 Vth만큼 줄어드는 셈입니다.

이는 저전력에서 큰 차이입니다.

<Fig. 9.48>

다른 sensing 방법으로는 Fig. 9.48처럼 deep triode region의 MOSFET을 사용하는 것이 있습니다.

여기서 M7과 M8이 서로 같은 transistor로서 둘다 deep triode region에 있고, Rtot = Ron7||Ron8은 (9.49)와 같습니다.

이 회로에서 output CM level을 sensing하는 방법은, Vout2+Vout1이 증가하면 Rtot이 감소하고, |Vout2-Vout1|이 증가하면 Ron7과 Ron8의 차이가 벌어지는 걸로 Vout,cm을 sensing하는 겁니다.

그런데 Fig. 9.48(a) 같은 경우에도 M7과 M8로 인해 output swing이 감소합니다.

Vout,min=Vth7,8같지만, 그렇게 되면 두 tr이 deep triode region에서 동작한다는 조건이 성립하지 않게 됩니다.

Fig. 9.48(b)처럼 Vout1=Vth이고 Vout2는 Vout,cm-Vth만큼 증가하면, M7이 saturation이 되어 의도한 sensing 기법이 통하지 않습니다.

또 다른 sensing 방법입니다.

여기서는 M2와 M4에 흐르는 small-signal current가 각각 gm/2*Vout1과 gm/2*Vout2라서, Icm=gm/2*(Vout1+Vout2)입니다.

그런데 이 회로의 단점은, Vout1과 Vout2의 swing이 크다면, nonlinearity에 의해 Icm이 Vout1+Vout2에 비례하지 않게 된다는 것입니다.

CM Feedback 방법

이제 sensing해온 CM level을 reference와 비교하고, op amp의 bias network에 error를 전달하는 feedback을 보겠습니다.

Ve amp가 Vout,cm과 Vref의 차이를 감지해서 NMOS current source로 전달하는 negative feedback을 걸어줍니다.

만약 Vout1과 Vout2가 증가하면, Ve도 증가해서 M3, M4의 drain current를 증가시키고, output CM level을 떨어뜨립니다.

Loop gain이 크면, feedback network가 output CM level이 Vref에 도달하도록 force할 수 있습니다.

여기서는 NMOS current source에 feedback을 걸었는데, PMOS current source에도 feedback을 걸어줄 수 있습니다.

Folded cascode amp에서는 CM feedback이 input differential pair의 tail current를 조절하는 식으로 구현됩니다.

Vout1과 Vout2가 증가해서 output CM level이 증가하면 Ve의 증가로 tail current(Id1, Id2)가 증가해서, M5, M6의 drain current가 감소하고 output CM level이 감소하여 복구됩니다.

아까 봤던 Fig. 9.48처럼 triode device M7, M8을 사용하는 CMFB의 연장선입니다.

M7과 M8이 M5, M6의 bias current를 잡아주고 있습니다.

그리고 Vout은 Id5, Id6가 Id9, Id10과 같도록 M7, M8을 biasing합니다.

Vout1과 Vout2가 증가하면, (9.49)에 의해 Ron7||Ron8이 감소하고, M5, M6의 Vgs가 증가했으니 Id5, Id6가 증가해서, Vout1, Vout2가 감소합니다.

Id9=Id10=Id라 하면, Ron7||Ron8 = (Vb-Vgs5)/2Id (9.50)이고, Vout1+Vout2가 (9.51)과 같습니다.

여기에 Vgs5 식을 대입해서 output CM level을 구할 수 있습니다.

<이 회로의 단점>

- Output CM level이 device parameter에 대한 식입니다. 그러면 PVT의 영향을 많이 받습니다.

- Ron7||Ron8에 의해 output voltage swing에 제한이 생깁니다.

- Output swing 감소를 줄이기 위해 M7, M8의 W를 크게 쓰면, output에서 capacitance가 커집니다.

Feedback을 input differential pair의 tail current에 가하면 두 번째 문제인 output swing 제한을 줄일 수 있습니다. (다음 회로)

Input differential pair의 tail current에 feedback을 가한 회로입니다.

Fig. 9.56(a)는 Fig. 9.54의 회로를 변형한 것으로,

output level이 device parameter의 영향을 덜 받도록 하고, Vb에 대한 민감성을 낮추는 방법입니다.

M15와 M9의 W/L이 같고, M16의 W/L과 M7, M8의 W/L을 합한 값이 같다고 하면, Vout,cm=Vref일 조건은 Id9=I1일 때입니다.

즉, Id9와 I1의 비교를 통해 Vout,cm과 Vref를 비교할 수 있습니다.

이전 예시와 달리 resistor를 쓰지 않고 Vout,cm을 sensing할 수 있는 것입니다.

Fig. 9.56(b)와 같이 이를 구체화할 수 있습니다.

그런데 이 회로에서는 Vds15≠Vds9이기 때문에, channel-length modulation으로 인해 CMFB에 오차가 생깁니다.

- Vds15≠Vds9인 이유: (M15와 M9는 Vdd~gnd path에 있는 tr 개수가 다름) Vds15=Vdd-(diode로 이한 Vds)-Vov,16이고, Vds9=Vdd-Vov4-Vov1-Vov7이기 때문에 Vds15가 Vds9보다 대략 Vov만큼 크다고 할 수 있습니다.

- Channel-length modulation으로 인한 CMFB 오차: Channel-length modulation을 포함한 Id 식을 참고하면, M15와 M9의 Vgs(Vref와 Vout,cm)가 같다고 해도 Vds15, Vds9가 다르면 Id가 서로 달라져서 CMFB가 Vref와 Vout,cm을 제대로 비교하지 못하게 됩니다.

따라서 M15 쪽에 M1, M2 역할을 하는 M17, M18을 추가해서 M15와 M9의 drain 전압을 같게 맞춰주면, Vds15=Vds9가 되어 CMFB를 제대로 동작시킬 수 있습니다.

Fig. 9.58(a)에서는 output CM level이 Vdd-|Vgs3,4|로 well-defined돼있긴 하지만, voltage gain이 낮습니다.

Gain을 높이기 위해서는, M3, M4가 differential signal에 대해 current source처럼 동작해야 합니다.

그래서 Fig. 9.58(b)처럼 회로를 바꿔서, Vout1과 Vout2의 differential한 변화에 대해 node P가 virtual ground이도록 했습니다.

이때 gain은 gm1,2(ro1,2||ro3,4||Rf)이고, Rf >> ro1,2||ro3,4이도록 설정해서 Rf로 빠지는 전류를 줄입니다.

저전력으로 동작하게 할 때는 Fig. 9.58(c)처럼 node P에 current source I1을 달아줍니다.

Vp는 Vdd-|Vgs3,4|로 같지만, M3, M4의 drain voltage가 Vp보다 I1Rf/2만큼 높아서 output swing이 커지는 효과가 있습니다.

Two-Stage Op Amp에서의 CMFB

다음은 two-stage op amp에서의 CMFB입니다.

세 가지 방법을 소개하는데,

<Fig. 9.60(b)>

첫 번째 방법은 Vout1과 Vout2를 sensing해서 Vb2만 조절하는 것입니다.

예를 들어, Iss가 Id3+Id4보다 작으면

Vx와 Vy가 높아지고

Id3+Id4=Iss가 되도록 M3, M4가 triode에 빠져버립니다.

또, Vx와 Vy가 높아지니까 M5와 M6의 |Vgs|가 감소해서, M5~M8에 흐르는 전류가 너무 작아지는 문제도 있습니다.

<Fig. 9.60(c)>

두 번째 방법은 Vout1과 Vout2를 sensing한 결과를 Iss로 보내는 것입니다.

예를 들어, Vout1과 Vout2가 너무 높다면,

Ae가 Iss를 줄여서 Vx와 Vy가 높아지도록 해서,

|Id5|와 |Id6|를 줄여서 Vout1과 Vout2가 작아지도록 합니다.

여기서는 M5와 M6가 X와 Y에서의 CM level을 sensing해서, loop 하나로 Vout1, Vout2 뿐만 아니라 Vx, Vy도 조절할 수 있습니다.

<Fig. 9.61>

그런데 이 두번째 방법에도 critical한 단점이 있습니다.

이 CMFB loop에는 최소 4개의 pole이 있습니다.

- X 또는 Y에 하나,

- Vout1, Vout2에 하나,

- Error amp에 최소 하나,

- Rcm(충분히 클 때)이 error amp의 input capacitance와 만드는 pole 하나입니다.

- 따라서, M1과 M2의 source에 있는 pole을 세지 않고도 CMFB loop에 pole이 3~4개가 있는데, pole이 이렇게 많으면 loop이 stable하기 어렵습니다.

이런 stability 이슈를 피하기 위해서, 2-stage op amp의 두 단계에 CMFB를 각각 적용하는 게 세 번째 방법입니다.

R1과 R2가 첫 번째 stage의 CMFB를 담당하고, R3와 R4가 두 번째 stage의 CMFB를 담당합니다.

- R1과 R2는 |Id3|=|Id4|=Iss/2이도록 Vgs3,4를 조절합니다.

- R3과 R4는 Id7=Id8=|Id5|=|Id6|이도록 Vgs7,8을 조절합니다.

Vgs3,4=Vgs5,6이라서 모든 drain current는 Iss로부터 복사되고,

이 회로의 differential voltage gain은 gm1(ro1||ro3||R1)gm5(ro5||ro7||R3)입니다.

만약 첫 번째 stage가 telescopic cascode라면, CMFB를 적용했을 때 이런 형태가 됩니다.

9.8. Input Range Limitations

Input Range 제한

Op amp의 input range는 제한적인데, input CM voltage가 넓은 범위에서 변할 수 있어야 하는 경우가 많습니다.

예를 들어, Fig. 9.65의 unity gain buffer에서는 input CM level이 너무 낮아지면, NMOS differential pair(M1, M2)의 bias current가 줄어들어 gm이 감소합니다.

이를 해결하기 위해 Fig. 9.66에서는 NMOS와 PMOS differential pair를 둘다 써서, 한쪽이 ‘죽으면‘ 다른 쪽이 활성화되는 구조를 사용합니다.

즉, input CM이 낮아서 NMOS differential pair가 꺼지면 PMOS differential pair가 작동하고,

반대로 input CM이 높으면 NMOS differential pair가 정상 작동합니다.

하지만, 이 기법을 쓰면 input CM 변화에 따라 전체 gm이 Fig. 9.67과 같은 양상으로 변하는 문제가 생깁니다.

이는 gain, 속도, noise에 영항을 줄 수 있습니다.

따라서, NMOS와 PMOS differential pair를 조합해 input CM range를 확장할 때, gm 변화를 최소화하는 추가적인 gm 제어 기법이 필요합니다.