참고: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second Edition

Chapter 9 - Operational Amplifiers (pg. 390~405)

9. Operational Amplifiers

9.9. Slew Rate

Slew Rate

다음은 op amp의 large-signal 특성 중 하나인 “slewing”에 대한 얘기입니다.

Fig. 9.68의 simple한 RC network에서, Vin이 크기 V0의 step function이면, Vout=V0/τ *[1-exp(-t/τ)]입니다.

Vout의 시간에 대한 기울기는 V0에 비례하는 것을 볼 수 있죠.

즉, 다른 parameter는 일정하고 input 크기가 2배되면, output 기울기도 2배, 최종 output도 2배가 됩니다.

RC network에서 Vout이 V0에 비례했던 것이 linear feedback system에도 똑같이 관찰됩니다.

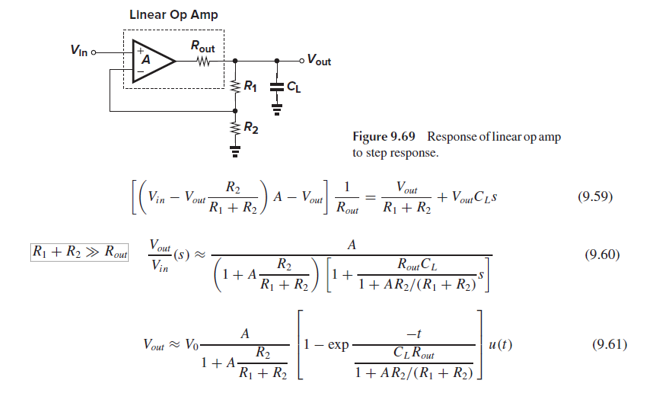

Fig. 9.69의 linear op amp에서, Vout node에서 KCL을 쓰면 (9.59)가 됩니다.

R1+R2>>Rout이라 가정하면 Vout/Vin(s)는 (9.60)으로 정리됩니다.

Low-frequency gain A와 time constant RoutCl이 둘다 1+A*R2/(R1+R2)로 나뉘어진 것을 볼 수 있습니다.

따라서 Vout의 step response는 (9.61)이고, linear feedback system에서도 Vout이 V0에 비례하는 것을 확인할 수 있습니다.

이러한 response를 “linear settling”이라고 합니다.

Linear op amp가 아닌 실제 op amp에서는, input 크기 V0가 증가할수록 step response가 이론적인 식(9.61)보다 커집니다.

Fig. 9.70에서 보는 것처럼, input 크기가 작을 때는 Vout이 exponential한 그래프를 따라가는데, input이 커질수록 이를 벗어나서 일정한 기울기를 갖는 ramp가 생깁니다.

Ramp가 나타날 때, op amp에 “slewing”이 나타난다고 하고, ramp의 기울기를 “slew rate”라고 합니다.

Op Amp의 Slew Rate

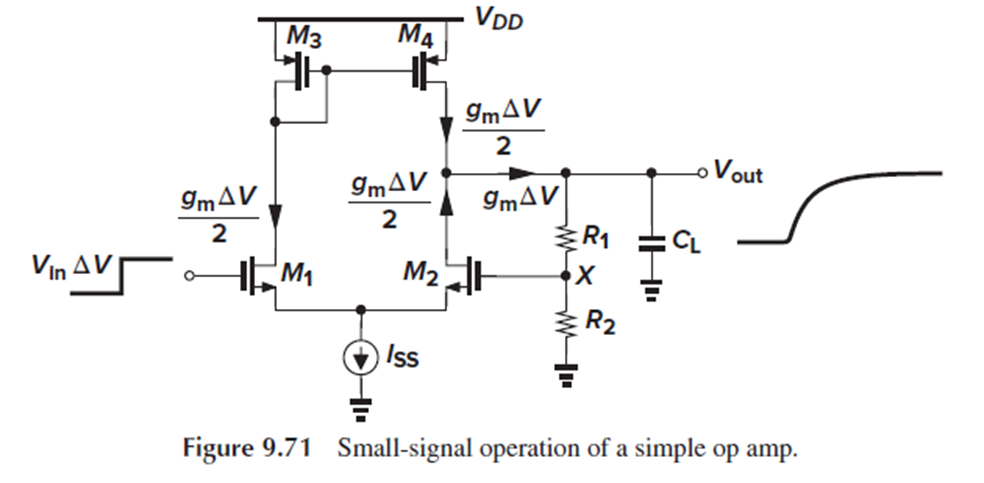

Fig. 9.71의 op amp에서는, 만약 Vin이 ΔV만큼 증가하면, 결과적으로 Vx가 증가하여 Vg1과 Vg2의 차이가 줄어듭니다.

- Vin이 ΔV만큼 증가하면, Id1은 gmΔV/2만큼 증가하고, Id2는 gmΔV/2만큼 감소합니다.

- Current mirror에 의해 Id4가 gmΔV/2만큼 증가해서, Iout은 gmΔV만큼 증가합니다.

- 이 전류가 CL을 충전시키면서 Vout이 증가하고, Vx, 즉 Vg2도 따라서 증가합니다.

- Vg1과 Vg2의 차이가 줄어들어 op amp의 Iout도 줄어들고, Vout이 이상적인 개형(9.61)을 따르게 됩니다.

Slewing이 Nonlinear한 현상인 이유

이번에는 Vin이 너무 커질 때와, 너무 작아질 때의 회로 동작을 보겠습니다.

<Fig. 9.72(a)>

Vin이 너무 커지면, M1에 Iss가 다 흐르고, M2는 꺼집니다.

그러면 current mirror에 의해 M4에 Iss가 흐르고, 이것이 Vout으로 흘러 CL을 충전시킵니다.

이때 Vout이 Iss/CL의 slew rate로 증가하고, Vx도 증가합니다.

Vin과 Vx의 차이가 줄어들어서, M2가 다시 켜지고, 회로가 다시 linear하게 동작하게 됩니다.

<Fig. 9.72(b)>

반대로 Vin이 너무 작아지면, M2에 Iss가 다 흘러서, CL로부터 Iss를 빼오는 꼴이 되고 Vout이 slew rate Iss/CL로 감소합니다.

따라서 Vx가 감소해서 Vin과의 차이가 줄어들고, M1이 다시 켜져서, 회로가 linear하게 동작하게 됩니다.

여기서 주목할 점은, Vin이 변하더라도 slew rate가 Vin과 무관한 값이라는 것입니다.

Vin이 2배 증가하더라도 slew rate는 2배 변하지 않기 때문에, slewing은 nonlinear한 현상이고, 회로에서 원치 않는 현상입니다.

특히, 큰 신호를 다루는 high-speed 회로에서, 전류가 작아서 output이 원하는 속도로 변하지 못하는 slewing이 나타납니다.

Small-signal bandwith가 크더라도 실제 동작 속도가 slewing 때문에 제한되는 것입니다.

만약 증폭해야 하는 신호가 V0sin(ω0t) 형태라면, output이 이 빠른 신호를 왜곡 없이 따라가기 위해 slew rate는 반드시 V0ω0 이상이어야 합니다.

Telescopic Op Amp의 Slew Rate

다음 예시로, Fig. 9.74(a) telescopic op amp의 slew rate를 구해봅시다.

큰 differential input이 가해지면, M1 또는 M2가 꺼져서, Fig. 9.74(b)처럼 됩니다.

M5~M8은 cascode current source로, M7~M8이 bias current를 잡아주고, M5~M6이 cascode transistor로 동작하면서 output resistance를 증가시켜서 전류가 일정하게 유지됩니다.

M2가 꺼지면 M1에 Iss가 흘러야 하는데, 부족한 전류를 CL로부터 끌어옵니다.

그리고 M2가 꺼져있으니 M2쪽 CL에 Iss/2가 흐릅니다.

그러면 Vout1과 Vout2의 slew rate가 ±Iss/(2CL)이 되고, Vout1-Vout2의 slew rate는 Iss/CL이 됩니다.

Folded-Cascode Op Amp의 Slew Rate

Fig. 9.75는 single-ended output을 가진 folded-cascode op amp의 slewing 특성입니다.

Fig. 9.75(a)와 (b)는 각각 input이 positive와 negative step을 가질 때의 회로입니다.

<Fig. 9.75(a)>

M9, M10이 Ip를 공급하고 있고, input이 큰 positive step을 가지면 M1에 Iss가 흘러서 M3에는 Ip-Iss, M4에는 Ip가 흐릅니다.

M5~M8에 같은 전류 Ip-Iss가 흘러야 하므로 CL로 Iss가 흘러 CL을 충전시킵니다.

<Fig. 9.75(b)>

반대로 input이 큰 negative step을 가지면 CL로부터 Iss가 빠져나옵니다.

이때, Ip≥Iss이도록 설계해야 output node에 흐르는 전류가 Iss로 제한되어, slew rate를 Ip와 무관하게 Iss/CL로 나타낼 수 있습니다.

만약 Ip<Iss이면 output node에 흐를 전류가 부족해서 slew rate가 Ip/CL로 결정되어, Ip에 의존하게 됩니다.

따라서, 일반적으로 Ip≥Iss, Ip≈Iss로 설계하는데, 이때 Ip-Iss가 너무 작으면 M5~M8이 triode에 빠질 수 있으므로 적당한 margin을 두어야 합니다.

Fig. 9.75(a)에서 만약 Iss>Ip라면, M3가 꺼지고 Vx가 끌려 내려가서, M1과 tail current source Iss가 triode에 빠지게 됩니다.

그래서 Id1이 감소하면 M2가 켜지면서 M4가 전류를 공급하고, M3가 다시 켜져서 Vx가 상승하게 됩니다.

따라서 Fig. 9.76과 같이, Vx가 줄어들었다가 다시 증가하는 swing 동안 settling이 늦춰지는 현상이 나타납니다.

Clamp Circuit

이렇게 slewing 중에 Vx나 Vy가 훅 떨어지는 문제를 해결할 수 있는 방법이 “clamp” transistor M11, M12를 추가하는 것입니다.

<Fig. 9.77(a)>

Vx가 낮아져서 M3가 꺼지면, M12가 켜져서 Vx에 전류를 공급해서, Vx가 너무 낮아지지 않게 보호합니다.

반대로 Vy가 낮아지면, M11이 켜져서 Vy를 다시 높입니다.

따라서 이렇게 clamping을 하면 Vx, Vy가 과도하게 낮아지는 걸 막아서, tail current source Iss가 triode로 빠지는 것도 막을 수 있습니다.

결과적으로 회로가 더 빠르게 정상 상태로 복귀하고, settling time이 단축됩니다.

<Fig. 9.77(b)>

M11, M12를 Vdd에 직접 clamping한 것으로, Vx와 Vy가 Vdd와 더 가깝게 유지됩니다.

이때 보통 Vx와 Vy가 Vdd-Vthn보다 크기 때문에 정상적인 동작에서는 slewing이 발생하지 않고, M11과 M12는 주로 꺼져 있습니다.

M11, M12는 slewing이 발생할 때만 켜져서 Vx, Vy를 보호하는 역할을 합니다.

High-Slew-Rate Op Amps

Fig. 9.78(a)에서 Vin이 인가되지 않는 상태에서는 Id1=I0인데, Vin이 negative step이면 M1이 꺼지고, I0이 CL로 흐릅니다.

이때 slew rate는 I0/CL인데, |Id2|를 I0보다 증가시킨다면 slew rate를 빠르게 할 수 있습니다.

따라서 Fig. 9.78(b)처럼, Vin을 M2에도 인가해 주면 Vin이 감소해서 M1이 꺼지는 동시에, |Id2|는 증가합니다.

그런데 이 방법은 power supply rejection이 나쁘다는 단점이 있습니다.

M2의 |Vgs2|=Vdd-Vin으로 |Id2|와 Vout이 Vdd의 영향을 받기 때문입니다.

그래서 다른 구조를 더 알아볼 것입니다.

우리는 Ib를 Vin에 따라 조절하고 싶습니다.

앞선 예시처럼, Vin이 감소하면 Ib가 증가해서 Vout의 slew rate를 빠르게 하는 식으로 말이죠.

<Fig. 9.79(a)>

앞의 Fig. 9.78(a)의 Vb를 M3을 써서 current mirror로 구현했습니다.

<Fig. 9.79(b)>

Ib가 Vin에 따라 조절되도록 하기 위해, M4를 추가해서 Ib를 common-source 구조의 bias current로 만들어 봤습니다.

그런데 이 회로에서는 Vin이 감소하면 Ib 역시 감소해서 Vout의 slew rate를 개선하기에 적합하지 않습니다.

<Fig. 9.79(c)>

M2의 bias current를 Vin-으로, M4의 bias current를 Vin+로 조절하는 방법을 사용했습니다.

그러면 Vin+가 감소하고 Vin-이 증가할 때

- Id5, Id1, |Id8|, |Id4|가 감소하고,

- Id6, Id3, |Id7|, |Id2|는 증가하고,

- Vin-의 증가로 Id3는 증가하는데 Id4로부터 전류를 충분히 공급받지 못하니 load capacitance로부터 전하를 끌어오고,

- Id1은 감소하고 |Id2|가 증가하므로 |Id2|-Id1만큼이 load capacitance로 충전됩니다.

Fig. 9.79(b)와 (c)는 “push-pull” stage라고도 합니다. Load current source가 Vin에 따라 변하는 “active” pull-up device이기 때문입니다.

이를 “class-AB” amplifier라고 하기도 합니다. Bias current가 일정한 amplifier는 “class-A” amplifier입니다.

<Fig. 9.79(d)>

Input common-mode rejection을 개선하기 위해 M1과 M3, M5와 M6에 각각 tail current source Iss1과 Iss2를 추가한 것입니다.

Input transistor에 tail current source가 연결돼있지 않은 상태에서는 input common mode가 differential current에 그대로 영향을 미치지 않습니다.

만약 Vin+가 크게 증가하면, M1과 M5가 각각 Iss1과 Iss2를 모두 흡수합니다.

그러면 M2가 꺼지고, Vout1이 Iss1/CL의 slew rate로 떨어지고, Vout2는 L4=L8를 가정하면 Iss2/(W4/W8)/CL의 rate로 증가합니다.

따라서 differential slew rate는 [Iss1+Iss2/(W4/W8)]/CL입니다.

Push-pull action이 없었다면, slew rate는 Iss1/CL로 더 작았을 것입니다.

Push-pull 동작을 two-stage op amp의 두 번째 stage에 적용하면 높은 slew rate를 얻을 수 있습니다.

Fig. 9.80은 아까 본 Fig. 9.79(c)를 two-stage op amp의 두 번째 stage로 만든 것입니다.

이 구조의 voltage gain은 (9.80)입니다.

Differential input step이 충분히 커서 M9만(M10만) 켜진다면,

P에서의 capacitance가 작다는 가정 하에 Vp(Vq)가 빠르게 증가해서,

M5, M1이 빠르게 응답해 Id5, Id1(Id6, Id3)이 커지고,

결과적으로 output의 slew rate가 향상됩니다.

2-stage 구조를 사용하면 Vp가 Vdd에 가깝게 높이 증가해서 M5, M1에 큰 Id가 흐릅니다.

두 번째 stage를 단독으로 사용할 때는 M5, M1에 PMOS current source가 공급하는 bias current가 흐르는데,

2-stage 구조를 사용함으로써 더 큰 Id가 흐를 수 있어, 더 높은 slew rate를 얻을 수 있는 것입니다.

Power Supply Rejection

Op amp는 noisy한 line으로부터 supply를 받는 경우가 많아서, supply에 낀 noise를 “reject”할 수 있는 능력이 중요합니다.

Supply의 noise가 output에 얼마나 영향을 미치는지를 power supply rejection ratio(PSRR)로 나타냅니다.

PSRR은 (input부터 output의 gain)을 (supply부터 output의 gain)으로 나눈 것입니다.

Fig. 9.81의 경우, 낮은 주파수에서 PSRR은 gmn(rop||ron)으로 근사됩니다.

Vin부터 Vout까지의 gain은 gmn(rop||ron)이고, Vdd부터 Vout까지의 gain은 1/(rop||ron)이라서 PSRR이 gmn(rop||ron)^2이 되는데요.

책에서는 간략하게 gmn(ron||rop)로 근사시켰습니다.

이 회로의 경우, PSRR을 높이려면 gmn이나 (rop||ron)을 증가시켜야 합니다.

Noise in Op Amps

Fig. 9.84의 telescopic op amp의 경우, 낮은 주파수에서는 cascode device가 noise에 거의 기여하지 않습니다.

그래서 noise의 주 source는 M1~M2와 M7~M8입니다.

Unit bandwidth 당 input-referred noise voltage는 (9.88)과 같습니다.