참고: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second Edition

Chapter 12 - Bandgap References (pg. 523~535)

▼ 이전 글

PTAT, CTAT, Bandgap References, Start-Up, Temperature Coefficient(TC), Design Issues [Razavi][Ch12]

참고: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second EditionChapter 12 - Bandgap References (pg. 509~522)12. Bandgap ReferencesReference Generation앞서 본 회로들에서 reference current나 reference voltage 값은 변하지 않는

soobdal.tistory.com

12. Bandgap References

PTAT Current Generation

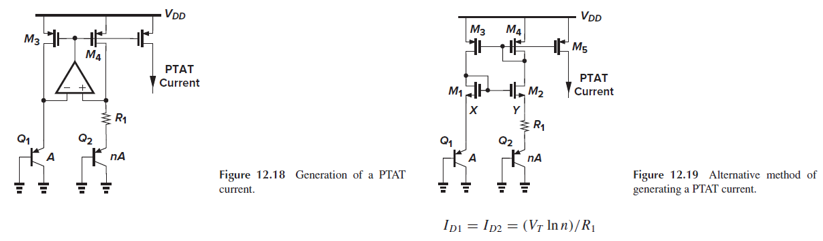

이전 글에서 언급했듯이, 이런 식으로 PTAT current를 만드는데, Fig. 12.18처럼 op amp를 써서 M3, M4의 Vgs를 같게 할 수도 있고, Fig. 12.19처럼 current mirror 구조를 써도 됩니다.

PTAT current를 만든 후, 이를 이용해 bandgap reference voltage를 만들 것입니다.

M1과 M2가 동일하고, M3, M4가 동일하다고 가정했을 때, Id1=Id2려면 Vx=Vy여야 합니다.

이때 Id1=Id2=(Vt*ln(n))/R1입니다.

실제 회로에서는 tr의 mismatch와 R1의 temperature coefficient 오차로 인해 Id5가 이상적인 값에서 멀어집니다.

저전력에서는 Fig. 12.18이 더 선호됩니다.

Fig. 12.18의 PTAT "current" 회로를 조금 바꾸면 bandgap reference "voltage"를 만들 수 있습니다.

Fig. 12.20처럼 base-emitter voltage에 PTAT voltage Id5*R2를 더해주면 (12.51)의 Vref를 얻을 수 있습니다.

TC=0이기만 하면 Vbe3와 Q3의 사이즈는 임의의 값으로 써도 됩니다.

실제로는 PMOS의 mismatch로 인해 Vout에 오차가 생깁니다.

Constant-Gm Biasing

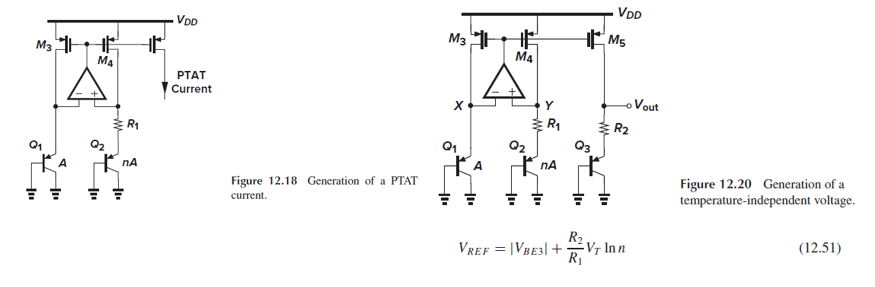

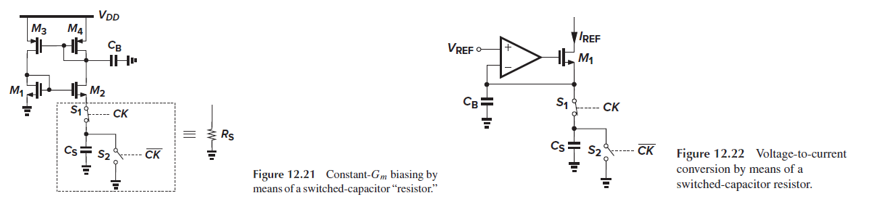

제일 초반에 Fig. 12.3 회로와 Iout 식을 봤었죠.

Iout 식으로부터 gm1을 이렇게 구해보면, gm 식 자체가 supply voltage와 MOSFET device parameter와 무관하긴 하지만, Rs가 온도와 공정에 의존합니다.

온도 같은 경우에는, temperature coefficient를 알면 온도 의존성을 제거할 수 있는데, 공정 variation 같은 경우에는 gm1의 accuracy를 떨어뜨려 버립니다.

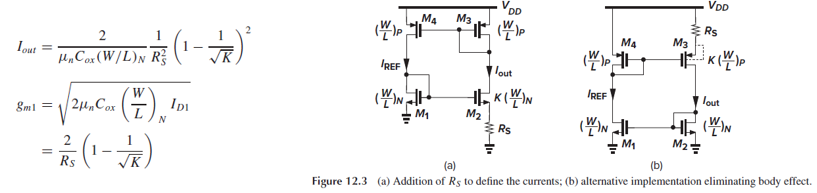

<Fig. 12.21>

만약 정확한 clock frequency를 만들 수 있다면, Rs를 switched capacitor로 대체하면 gm의 accuracy를 높일 수 있습니다.

Clock frequency를 fck라고 하면, M2의 source와 gnd 사이, Rs가 있던 자리에 switched capacitor를 넣어, average resistance가 1/(Cs*fck)짜리인 저항을 만드는 것입니다.

Switched capacitor를 쓰면 좋은 점은, 저항보다 cap 값이 variation이 적고, cap의 TC가 저항의 TC보다 훨씬 작다는 것입니다.

<Fig. 12.22>

Switched capacitor를 voltage-to-current conversion에 쓰면 회로의 accuracy를 높일 수 있다는, switched capacitor 활용 예시입니다.

Speed와 Noise 이슈

다음은 speed와 noise 이슈입니다.

Reference generator에는 high-speed op amp가 필요한 경우가 많습니다.

Fig. 12.23에서 만약 Vn이 빠르게 변하는데, op amp가 Vp를 빠르게 공급하지 못한다면 M5와 M6의 bias current의 transient response가 그림처럼 감소했다가 복원되는 형태가 됩니다.

Transient response를 좋게 하기 위해서는 high-speed op amp를 써야 합니다.

그런데, 저전력 reference 회로에서는 high-speed op amp를 쓰기 어려울 수 있습니다.

이럴 때 쓸 수 있는 방법은, Fig. 12.23처럼 node P에 큰 cap Cb를 달아서, 외부의 변화가 Cb에 의해 감쇠되도록 하는 것입니다.

Cb를 달 때 stability가 떨어지지 않도록 주의해야 하고요, Cb의 값을 크게 하는 것이 중요합니다.

왜냐하면, Vp에 disturbance를 전달하는 cap보다 Cb가 커야 disturbance가 Vp 대신 Cb에 전달될 것이기 때문입니다.

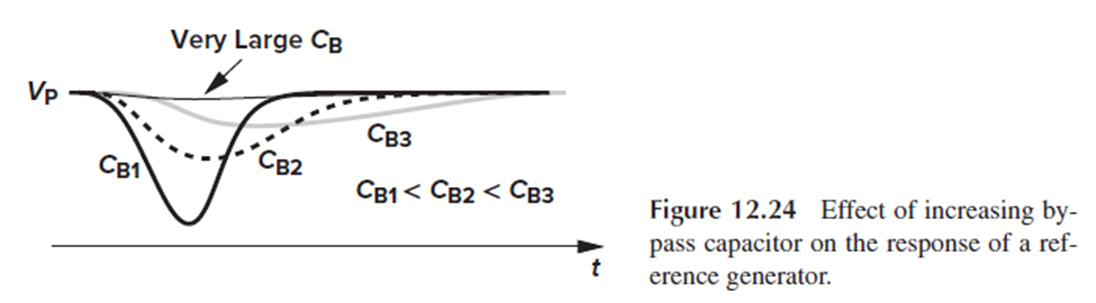

Fig. 12.24에서 보면, Cb가 충분히 크지 않으면 Vp의 transient response가 중간에 크게 감소했다가 돌아오는 구간이 생기는데, Cb가 충분히 크면 이런 현상이 나타나지 않습니다.

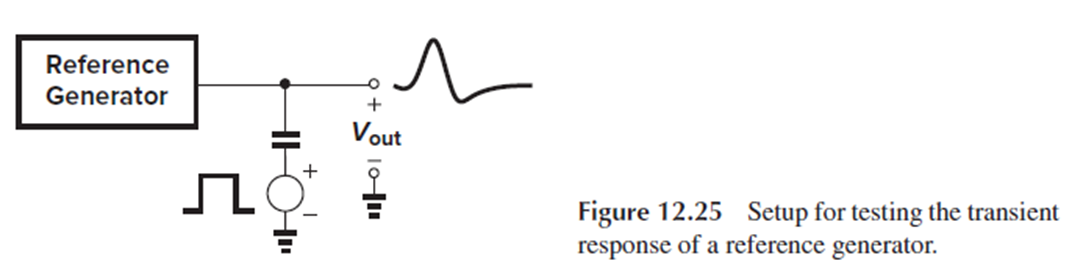

Reference generator의 transient response를 test해볼 때는 Fig. 12.25처럼, Vout에 disturbance를 주고, settling이 어떻게 일어나는지 관찰합니다.

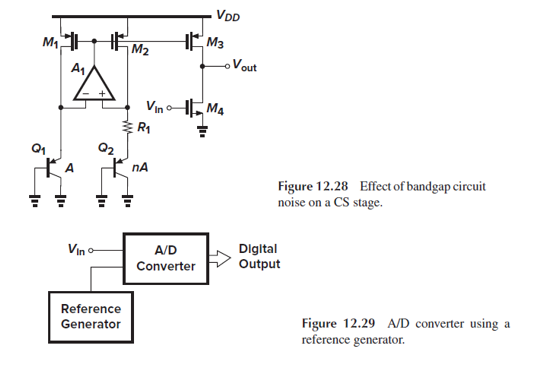

Fig. 12.28은 bandgap 회로가 CS stage의 load current source를 drive하고 있습니다.

Bandgap 회로의 전류를 n배해서 M3에 전달하고 있는데, 이때 bandgap 회로의 noise도 n배 되어 M3에 전달됩니다.

Fig. 12.29의 ADC에서는 bandgap voltage를 input reference로 쓰고 있는데, 이때도 reference의 noise가 input에 직접 더해집니다.

Reference generator에서 output noise voltage를 측정해 봅시다.

Op amp의 input에 Vn,op라는 noise를 줬을 때 output noise Vn,out이 얼마나 되는지 보겠습니다.

Fig. 12.30에서 small-signal drain current가 Vn,out/(R1+1/gmN)이니까, Vp는 여기에 1/gmP를 곱한 값이고, 따라서 input differential voltage는 Vp에 1/A0를 곱한 값입니다.

Node A부터 V+까지 KVL을 쓰고 근사하면, (12.65)의 결론이 나옵니다.

즉, reference에 쓰인 op amp의 noise가 output에 직접적으로 보인다는 것입니다.

저전력 Bandgap Reference

저전력에서는 조금 다른 reference 구조를 사용해야 합니다.

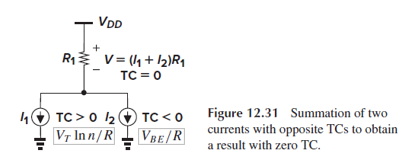

TC가 양수인 회로와 음수인 회로를 더해서 만드는 것은 이전과 같은데, 저전력에서는 이걸 전류로 만듭니다.

PTAT과 CTAT 전압을 R로 나눠서, TC>0인 PTAT 전류는 Vt*ln(n)/R로 만들고, TC<0인 CTAT 전류는 Vbe/R로 만들 수 있겠죠.

<Fig. 12.32(a)>

Fig. 12.32(a)에서 Id4는 PTAT current입니다.

Q2와 병렬로 저항 R2를 연결하면, R1에 추가로 |Vbe2|/R2가 흐릅니다.

그러나 Ic1≠Ic2가 되어 PTAT 특성이 방해를 받는다는 문제가 있습니다.

<Fig. 12.32(b)>

R2를 node Y에 R1과 병렬로 연결하고, node X에 R3를 연결하면 이 문제를 해결할 수 있습니다.

이때 Vdd 최소값은 Vbe1+|Vds3|입니다.

Op amp의 두 input에 들어가는 전류에 대해 (12.66)의 수식을 세울 수 있고, 이때 R2=R3이면 Ic1=Ic2입니다.

식 전개를 통해서 |Id4|를 구할 수 있습니다.

<Fig. 12.32(c)>

이 전류가 복사돼서 Vbg를 만들어내는데, Vbg는 TC가 0입니다.

(R2/R1)ln(n)≈17.2로 고릅니다.

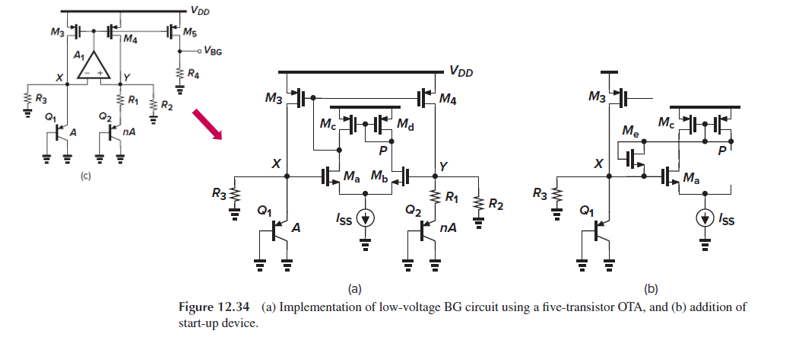

Fig. 12.34는 Fig. 12.32(c)의 op amp 부분을 five-transistor OTA로 그린 회로입니다.

<Fig. 12.34(a)>

여기서 주의할 점은, (Ma, Mb의 Vgs)+(Iss의 양단 전압)이 |Vbe1|을 넘으면 안 된다는 것입니다.

그리고 큰 tr을 써야 flicker noise와 offset을 줄일 수 있습니다.

<Fig. 12.34(b)>

Start-up을 위해 diode-connected NMOS인 Me를 추가했습니다.

Me를 추가하면 Vdd가 켜질 때 Vx가 바로 증가해서 Ma와 M3을 켤 수 있습니다.

Me를 X와 Vdd 사이에 직접 연결해도 됩니다.

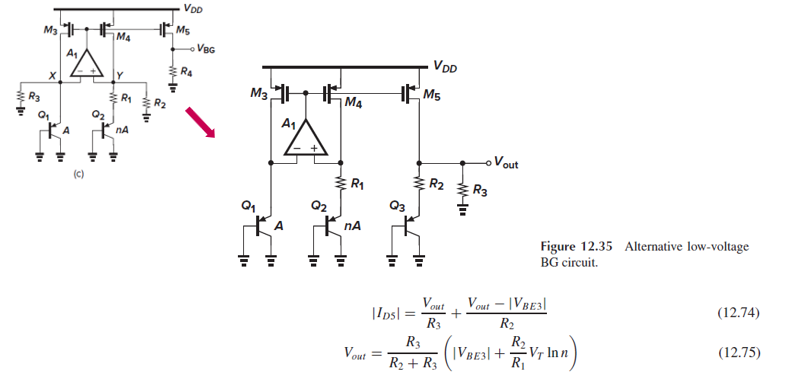

또 다른 저전력 bandgap 회로는 Vout에 저항 R3를 병렬로 연결한 것입니다.

Id5의 일부가 R3로 흐름으로써 bandgap voltage가 R3/(R2+R3)배만큼 줄어드는 효과가 있습니다.

High-Precision을 위한 Bandgap Reference

다음으로 high-precision 아날로그 시스템을 위한 bandgap reference를 알아보겠습니다.

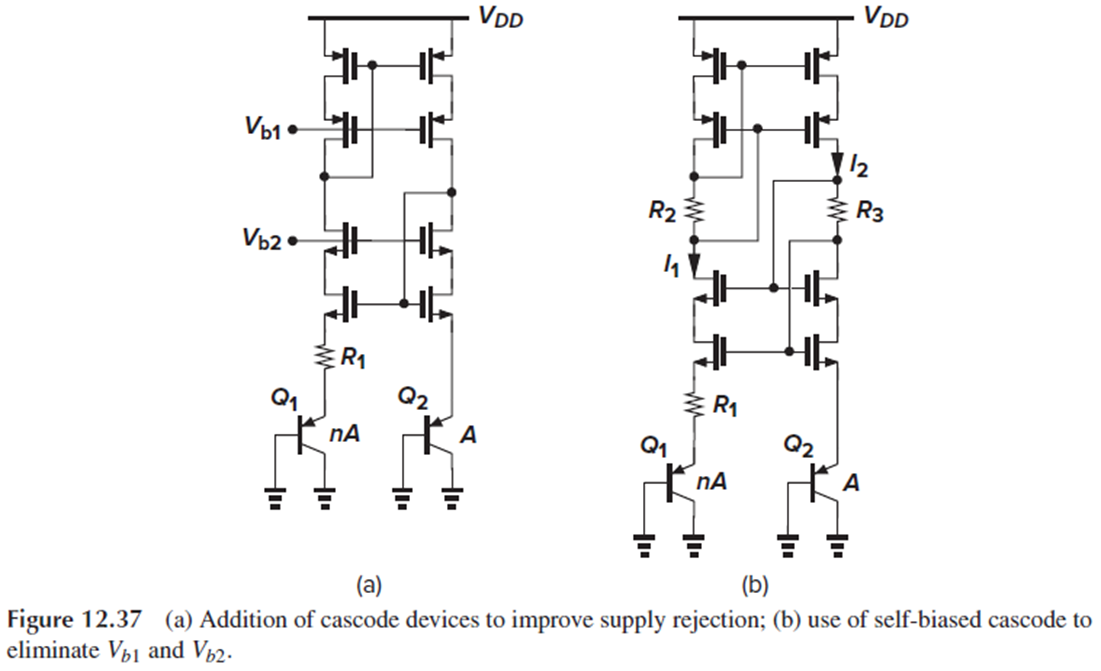

Fig. 12.36에서는 앞서 봤던 Fig. 12.19의 회로를 기본으로 해서, 각 branch에 Vbe(Q3, Q4)를 직렬로 연결해서 MOSFET mismatch를 줄였습니다. (이게 왜?)

이 구조에서는 큰 supply voltage가 필요하고, MOSFET의 channel-length modulation 때문에 supply dependence가 있습니다.

이걸 해결하기 위해서 Fig. 12.37(a)와 같이, 각 branch에 NMOS와 PMOS cascode를 추가했습니다.

Vb1과 Vb2가 따로 필요없도록 Fig. 12.37(b)처럼 회로를 만들 수도 있습니다.

Floating Reference

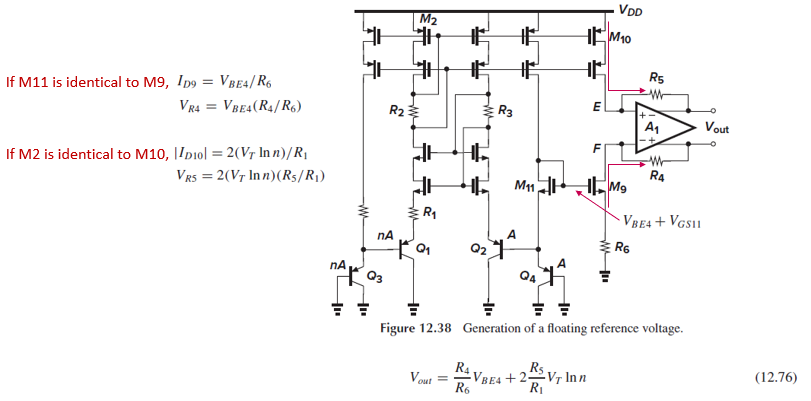

이 회로는 floating reference voltage를 만드는 회로입니다.

M9, M10의 drain current가 각각 R4와 R5로 들어가는데요.

M11이 M9의 gate voltage를 Vbe4+Vgs11로 잡고 있는데, M11과 M9의 사이즈가 같다면 R6 양단의 전압이 Vbe4가 됩니다.

따라서 Id9=Vbe4/R6, R4 양단의 전압은 여기에 R4를 곱한 값입니다.

또, 만약 M10과 M2의 사이즈가 같다면 |Id10|=2(Vt*ln(n))/R1이고, R5 양단의 전압은 여기에 R5를 곱한 값입니다.

Op amp에서 Ve≈Vf이므로, Vout은 이렇게 됩니다.

저항비와 n을 잘 골라서 temperature coefficient가 0이도록 만들 수 있습니다.

Supply Rejection 높이기

여기서 supply rejection을 높이고자 할 때, Fig. 12.39처럼 local supply인 Vddl을 Vdd로 사용할 수 있습니다.

Vddl은 reference Vr1과 Rr1, Rr2의 비율에 따라 정의되는데요, 이 Vr1은 supply 의존성을 줄이기 위해 core 안에서 만들어집니다.

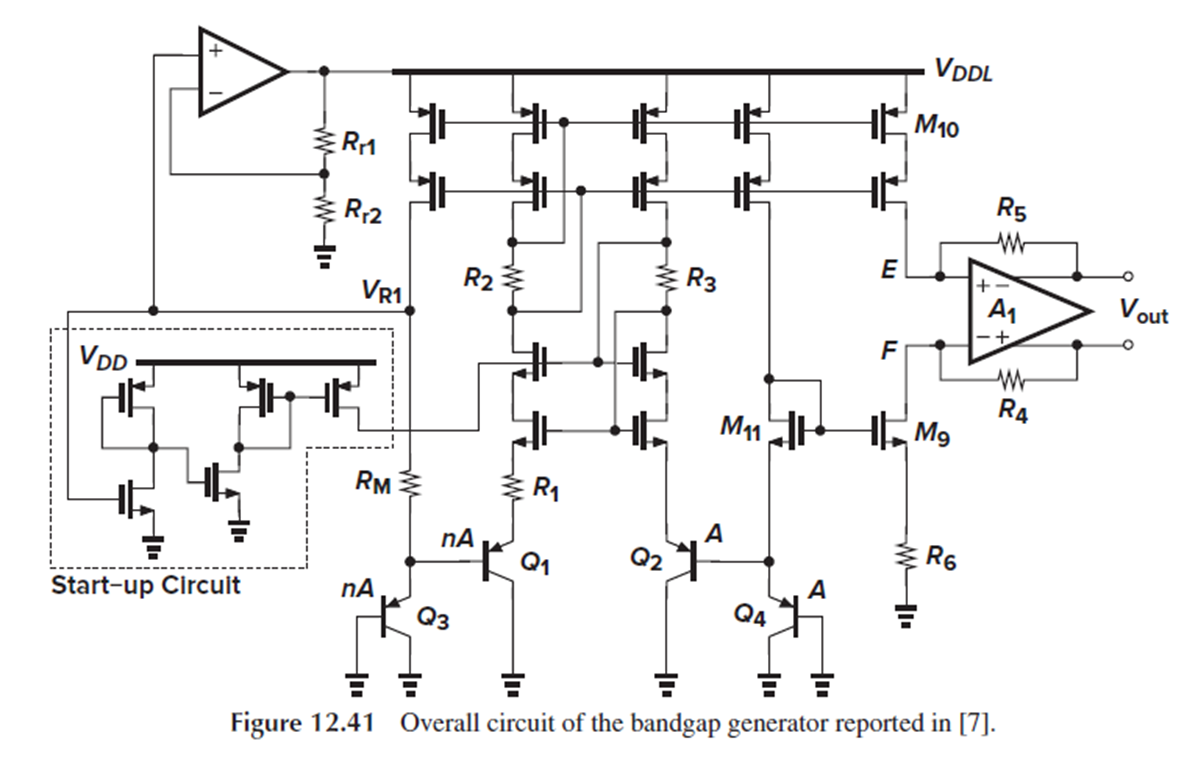

Bandgap Generator 최종 회로

지금까지의 내용을 종합한 bangap reference 회로는 이와 같습니다.