출처: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second Edition

Chapter 4 - Differential Amplifiers (pg. 100~102)

4. Differential Amplifiers

4.1. Single-Ended and Differential Operation

Single-Ended and Differential Signals

(Fig. 4.1(a)) Single-ended signal은 고정 전압을 기준으로 측정하는 신호인데, 주로 gnd를 기준으로 합니다.

Differential signal은 Fig. 4.1(b)의 node X와 Y처럼, 중심 전압을 기준으로, 크기는 같고 증감은 반대인 두 신호의 차를 의미합니다.

이 중심 전압을 “common-mode” (CM) level이라고 하고, common-mode level을 신호가 없을 때의 bias voltage라고 생각해도 무방합니다.

Fig. 4.1(b)에서 node X와 Y의 single-ended peak-to-peak swing은 2V0이고, differential peak-to-peak swing은 4V0입니다.

Differential Signaling for Sensitive Signals

Sensitive한 신호는 주변 환경에 의한 noise에 큰 타격을 입습니다.

그런데 differential signaling을 하면 single-ended signaling보다 주변 환경에 의한 noise의 영향을 덜 받을 수 있습니다.

Fig. 4.2(a)같은 single-ended signaling에서는 capacitive coupling으로 인한 noise가 신호에 그대로 생깁니다.

이에 비해, Fig. 4.2(b)의 differential signaling에서는 L2와 L3가 같은 noise를 받기 때문에, 두 신호의 차를 구하면 noise가 제거됩니다.

이를 두고, differential signaling이 common-mode noise를 “reject”한다고 합니다.

참고로, differential signaling에서 원하는 신호를 얻으려면, L2와 L3의 차를 1/2배 하면 됩니다.

- Capacitive coupling: cap을 사용하여 두 회로 간에 신호를 전달하는 방법

- 이때 cap은 입력 신호의 DC 성분을 차단하고 AC 성분만 전달함

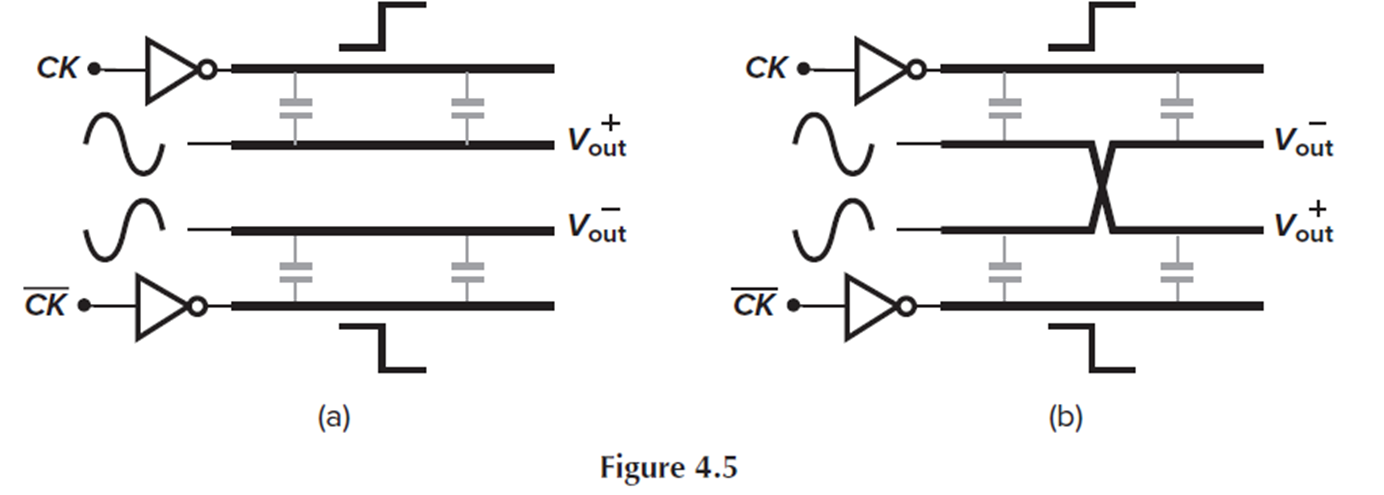

같은 맥락에서, Fig. 4.3(a)의 single-ended circuit에서는 VDD가 ΔV만큼 변하면 Vout도 거의 ΔV만큼 변합니다.

반면, Fig. 4.3(b)의 differential circuit에서는 VDD가 변하더라도, 회로가 symmetric하여 Vx와 Vy가 같은 영향을 받습니다.

따라서, Vx-Vy는 VDD의 변화에 큰 영향을 받지 않습니다.

Differential Signaling for Noisy Lines

아까는 output 신호가 differential한 경우를 봤는데, 이번에는 input signal이 differential한 경우를 보겠습니다.

Noise를 발생시키는 신호를 noisy line 혹은 “aggressor”, noise를 받는 신호를 sensitive signal 혹은 “victim”이라고 합니다.

Fig. 4.4에서는 clock signal이 L2와 L3에 differential하게 인가되고 있습니다.

그러면, CK에 의한 capacitive coupling과 CK bar에 의한 capacitive coupling이 L1에 영향을 미치는데, 두 효과가 서로를 상쇄하여 L1에 깔끔한 파형이 나옵니다.

Victim과 aggressor 둘 다 differential로 만들 수도 있습니다.

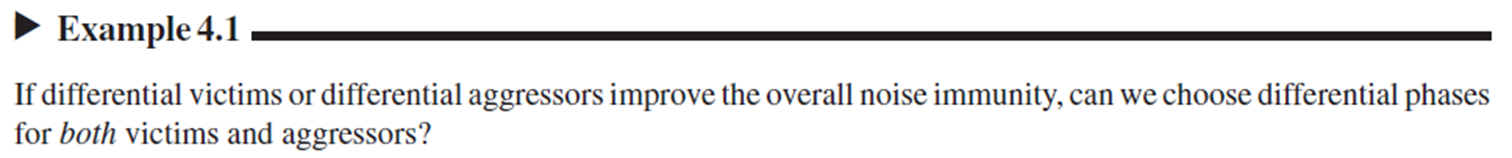

Fig. 4.5(a)처럼 differential victim들(Vout+, Vout-)이 differential aggressor에 둘러싸인 구조와, Fig. 4.5(b)처럼 differential victim들이 differential aggressor를 반반씩 따라가는 구조를 보겠습니다.

먼저 Fig. 4.5(a)의 경우, Vout+는 CK쪽 capacitive coupling에 영향을 받고, Vout-는 CK bar쪽 coupling에 영향을 받습니다.

Vout+과 Vout-가 서로 반대 polarity의 noise를 갖기 때문에, Vout+ - Vout-를 한다고 noise가 상쇄되지 않습니다.

Fig. 4.5(b)의 경우에는, Vout+와 Vout-가 CK와 CK bar 쪽 coupling의 영향을 반반씩 받아, 각 Vout에서 두 영향이 서로 상쇄됩니다.

따라서 Vout+, Vout- , Vout+ - Vout-가 모두 coupling의 영향을 받지 않습니다.

이런 구조를 “twisted pair”라고 합니다.

Differential Signaling Increases Voltage Swing

Fig. 4.3(b)의 X또는 Y에서 maximum output swing은 Vdd-(Vgs-Vth)입니다.

그런데 Vx-Vy의 peak-to-peak swing은 2[Vdd-(Vgs-Vth)]로 높아집니다.

즉, output swing이 높아지는 것이죠.

지금까지 differential 회로의 장점으로 supply noise rejection과 높은 output swing을 알아봤는데, 이것 말고도 biasing의 편리성과 linearity의 증가도 있습니다(Ch14: Nonlinearity and Mismatch에서 알아볼 것).

Differential 회로가 single-ended 회로보다 비록 공간은 2배를 더 차지하지만, 장점이 훨씬 많기 때문에 differential 회로를 사용합니다.

Amplifying Differential Signals

궁극적으로 differential signal로 amplifier를 만들기 위해서, 먼저 differential signal을 증폭하는 방법을 알아보겠습니다.

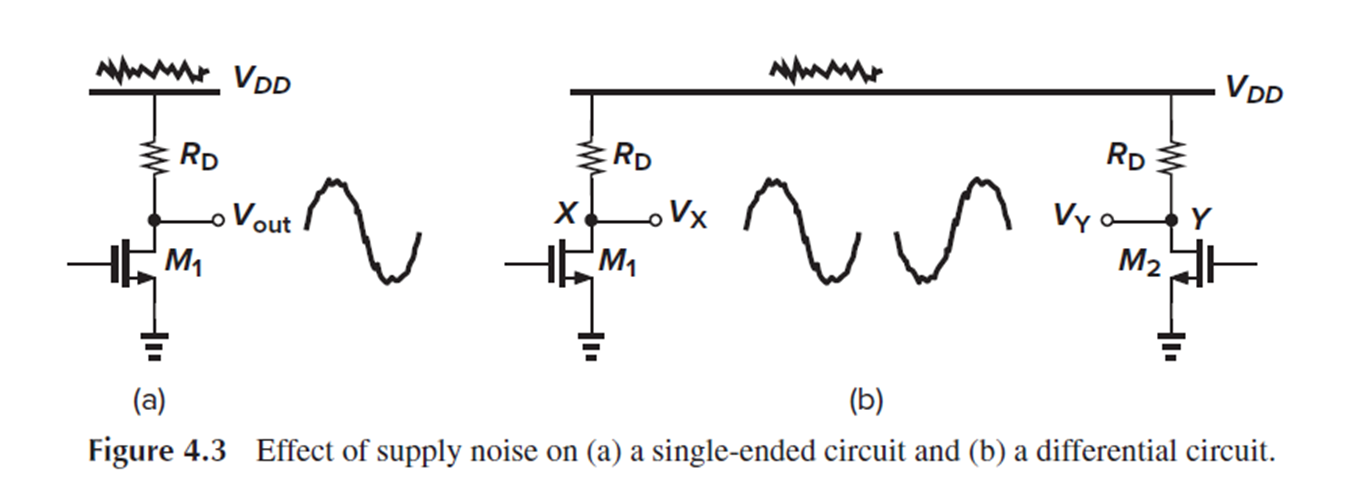

Fig. 4.6(a)의 simple differential circuit은 Vdd에 2개의 같은 single-ended path가 연결되어 있는 형태입니다.

(Fig. 4.6(b) 윗줄) Vin1과 Vin2는 Vin,cm을 중심으로 하는 differential signal입니다.

그러면 Vout1과 Vout2도 Vout,cm을 중심으로 하는 differential signal이 됩니다.

(Fig. 4.6(b) 아랫줄) 그런데 Vin,cm이 너무 낮을 경우, Vout이 clipping되는 문제가 생깁니다.

M1과 M2에 너무 작은 Id가 흘러 Vout1과 Vout2이 너무 커져, Vdd를 넘는 Vout이 clipping되어 버립니다.

Basic differential pair 구조를 통해 이 문제를 해결할 수 있습니다.

Basic differential pair의 구조, 동작 특성, common-mode 특성, large-signal과 small-signal 분석 등이 궁금하다면 아래 글을 읽어 주시길 바랍니다.

Basic Differential Pair - 동작 특성, Common-Mode Behavior, Output Swing, Large-Signal & Small-Signal 분석, Half-Circuit Co

출처: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second EditionChapter 4 - Differential Amplifiers (pg. 103~116) 4. Differential Amplifiers4.2. Basic Differential PairBasic Differential PairFig. 4.7의 basic differential pair 구조를

soobdal.tistory.com