참고: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second Edition

Chapter 4 - Differential Amplifiers (pg. 116~123)

4. Differential Amplifiers

4.2. Basic Differential Pair

4.2.3. Degenerated Differential Pair

Degenerated Differential Pair: Linearity 개선

Fig. 4.27(a)는 differential pair에 resistive degeneration을 단 회로입니다.

Common-source stage에 resistive degeneration을 달아서 linearity를 개선하는 것처럼, differential pair의 경우도 마찬가지입니다.

Differential pair에도 resistive degeneration을 추가하면 linearity가 개선됩니다.

Fig. 4.27(b)를 보면 resistive degeneration이 있을 때, 즉, Rs>0일 때, M1 또는 M2를 끄기 위한 differential voltgae의 절댓값이 ΔVin1에서 ΔVin2로 증가합니다.

이걸 증명해 보겠습니다.

Vin1-Vin2=ΔVin2일 때, M2가 on/off의 경계에 있게 되고 Id1=Iss가 된다고 가정해 봅시다.

이때 Vgs2=Vth이므로, Vp를 식으로 나타내면 (4.31)입니다.

이를 (4.32)와 같이 정리할 수 있고, saturation일 때의 Id 식으로부터 Vgs1-Vth를 변형하면 (4.33)이 됩니다.

Vin1-Vin2가 ΔVin2이고, Vgs1-Vth가 ΔVin1이므로 식은 (4.34)가 됩니다.

즉, linear input range가 ±Rs*Iss만큼 증가했다는 것을 알 수 있습니다.

Degenerated Differential Pair: Gain과 Linearity의 Tradeoff

이 회로의 gain은 half-circuit concept로 구할 수 있습니다.

Half-circuit concept에 대한 내용은 아래 글을 참고해 주세요.

Basic Differential Pair - 동작 특성, Common-Mode Behavior, Output Swing, Large-Signal & Small-Signal 분석, Half-Circuit Co

출처: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second EditionChapter 4 - Differential Amplifiers (pg. 103~116) 4. Differential Amplifiers4.2. Basic Differential PairBasic Differential PairFig. 4.7의 basic differential pair 구조를

soobdal.tistory.com

Half circuit은 각각 degenerated CS stage라서, gain이 (4.35)와 같습니다.

(4.35)를 보면, degeneration Rs로 인해 gain은 감소합니다.

따라서 differential amplifier에 resistive degeneration을 추가하면 gain과 linearity의 tradeoff가 있음을 알 수 있습니다.

Degenerated Differential Pair: Voltage Headroom 감소

Resistive degeneration이 있는 differential pair가 equilibrium 상태라고 했을 때, 두 Rs에서 각각 Rs*Iss/2만큼의 voltage drop이 생깁니다.

그럼에도 Id1+Id2=Iss가 되도록 하려면 input common-mode가 Rs*Iss/2씩 높아져야 하고, node X와 Y에서의 최소 전압(Vgs-Vth)도 Rs*Iss/2씩 높아지게 됩니다.

그러면 voltage headroom이 늘어나서 differential output swing은 Rs*Iss만큼 감소하겠죠.

Resistive degeneration을 Fig. 4.28처럼 추가하면 headroom을 잡아먹지 않습니다.

Tail current source Iss가 양쪽에 1/2Iss씩 달리고, degeneration은 두 current source 사이에 크기 2Rs로 달려 있습니다.

이러면 equilibrium일 때 Rs에 전류가 흐르지 않아서, headroom이 줄어들지 않습니다.

4.3. Common-Mode Response

다음으로 differential amplifier의 common-mode response에 대해 알아보겠습니다.

Differential amplifier의 중요한 특징 중 하나는, common-mode의 변화가 output에 나타나지 않도록 억제된다는 것입니다.

그런데 common-mode 변화가 output에 아예 나타나지 않으려면 differential pair가 완벽히 대칭적이고, current source가 ideal해야 합니다.

실제 회로에서는 두 조건이 모두 만족되지 않기 때문에, common-mode 변화의 일부가 output에 나타나게 됩니다.

Differential Pair의 대칭성 O, Current Source Ideal X

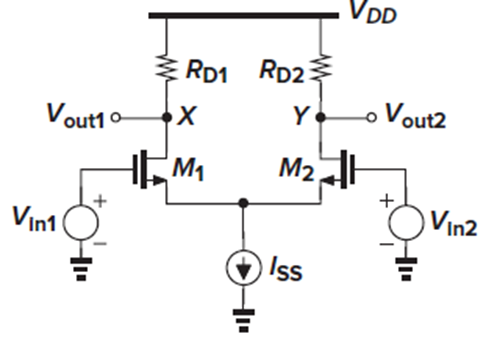

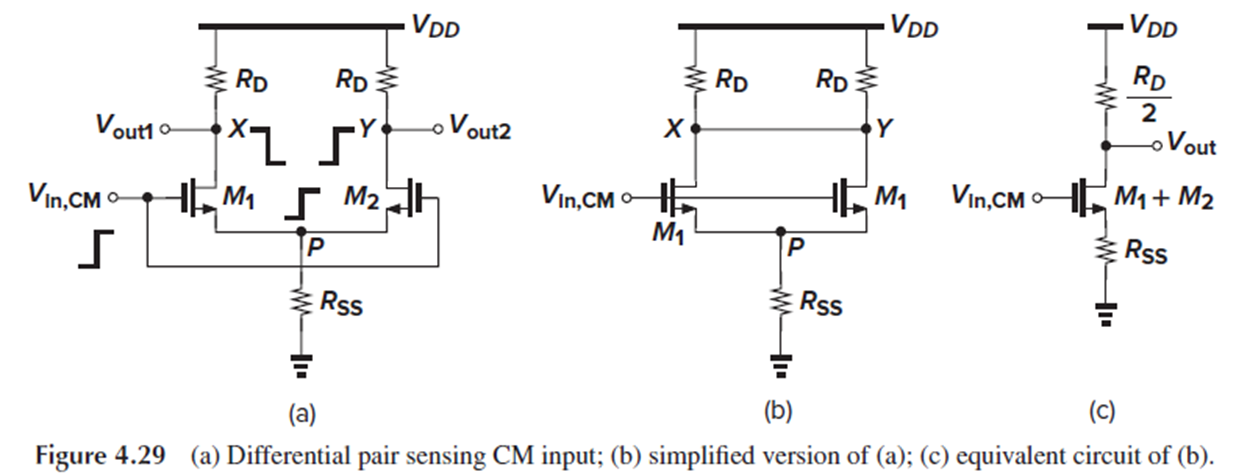

(Fig. 4.29(a)) 우선, differential pair는 완벽히 대칭적이지만 current source는 ideal하지 않은 경우를 보겠습니다.

Current source가 ideal하지 않아 finite한 output impedance를 가지고, 그 값을 Rss라 하겠습니다.

Vin,cm이 조금 증가하면, Vp가 증가해서(souce follower) M1과 M2에 흐르는 전류가 증가하고, Vx과 Vy는 감소합니다.

회로가 대칭적이라 Vx=Vy이니까, Fig. 4.29(b)처럼 두 node를 short시킬 수 있습니다.

그러면 M1과 M2가 병렬로 연결된 구조가 되어(W만 증가), Fig. 4.29(c)처럼 변형해 그릴 수 있습니다.

M1+M2는 M1(또는 M2)와 비교해 W만 2배 증가한 것으로, W/L이 2배라서 gm이 2배입니다.

따라서 이 회로의 common-mode gain은 (4.37)이 됩니다.

회로가 대칭적이더라도, current source가 ideal하지 않다면 input의 common-mode 변화가 common-mode gain을 바꾼다는 것을 알 수 있습니다.

Common-mode gain이 바뀌면 output CM level도 바뀌게 됩니다.

Differential Pair의 대칭성 X, Current Source Ideal X

근데 differential pair의 대칭성마저 깨진다면, 더 큰 문제가 발생합니다.

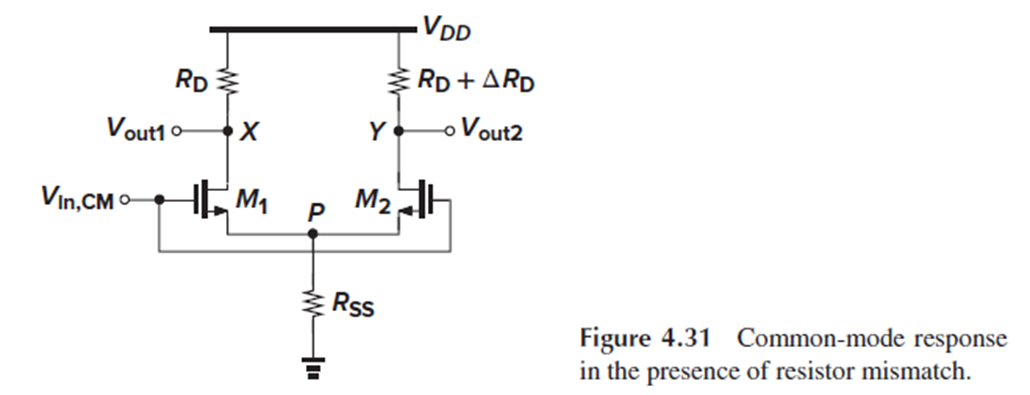

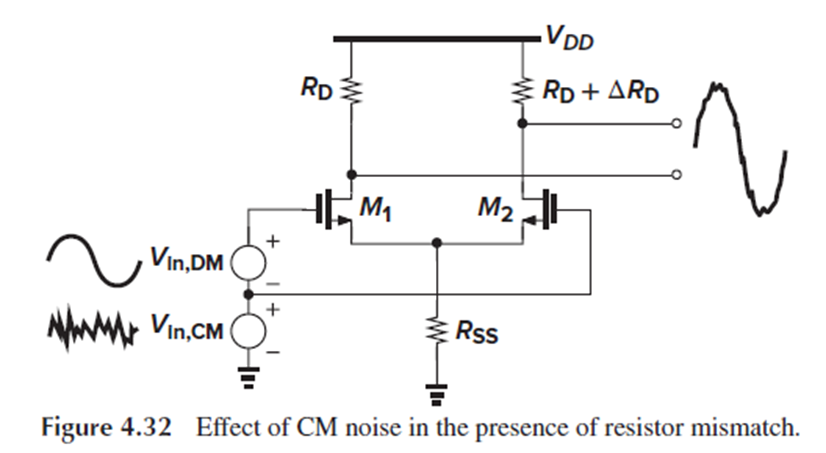

Fig. 4.31에처럼 Rd1=Rd, Rd2=Rd+ΔRd로 대칭적이지 않고, current source도 ideal하지 않은 differential pair를 보겠습니다.

Vin,cm을 변화시킬 때, M1과 M2는 Vp를 output으로 하는 source follower로 동작합니다.

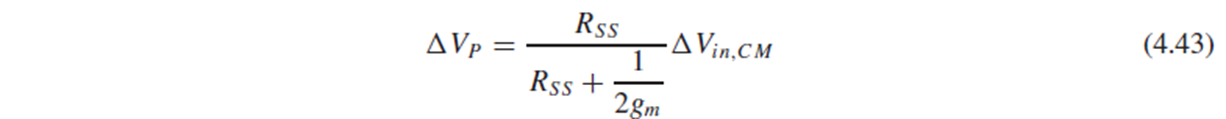

따라서 Vin,cm의 변화에 따른 Vp의 변화는 (4.43)과 같이 나타납니다.

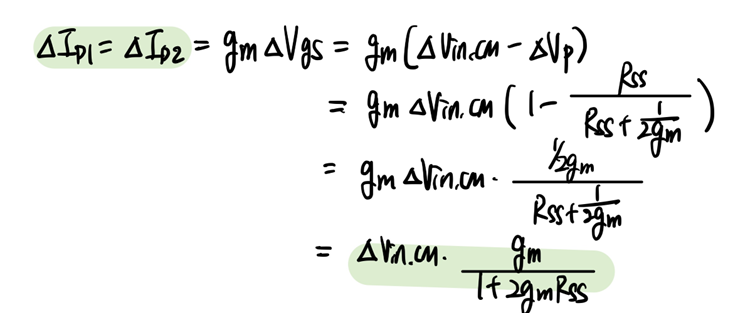

M1과 M2는 같으므로 두 MOSFET에 흐르는 전류는 아래와 같습니다.

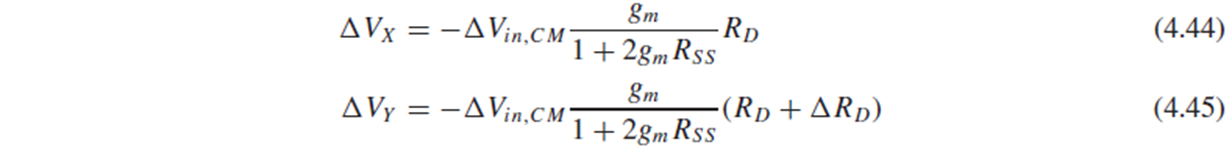

따라서 Vin,cm의 변화에 따른 Vx와 Vy의 변화는 (4.44), (4.45)와 같이 나타납니다.

Vin,cm은 이상적으로 output에 영향을 미치지 않아야 하는데, differential pair의 대칭성이 깨지면 output에 ΔVin,cm에 비례하는 변화가 나타나 버리는 것이 핵심입니다.

Noisy Vin,cm + Vin,dm

실제 회로와 비슷하게 Vin,cm에 noise가 있고, Vin,dm도 가해지는 경우로 일반화하해 봅시다.

이 경우, Vin,cm의 noise 때문에 Vin,dm에 의해 증폭된 신호에도 noise가 생깁니다.

아까 differential pair가 대칭적일 때는 common-mode gain이 바뀌어서 output CM level이 바뀌는 문제가 생겼는데, differential pair의 대칭성이 깨져서 input CM variation이 output에 전달되는 것이 좀더 심각한 문제입니다.

따라서, differential pair의 대칭성, mismatch 문제를 위주로 common-mode response를 다루는 것이 중요합니다.

Common-Mode to Differential-Mode Conversion

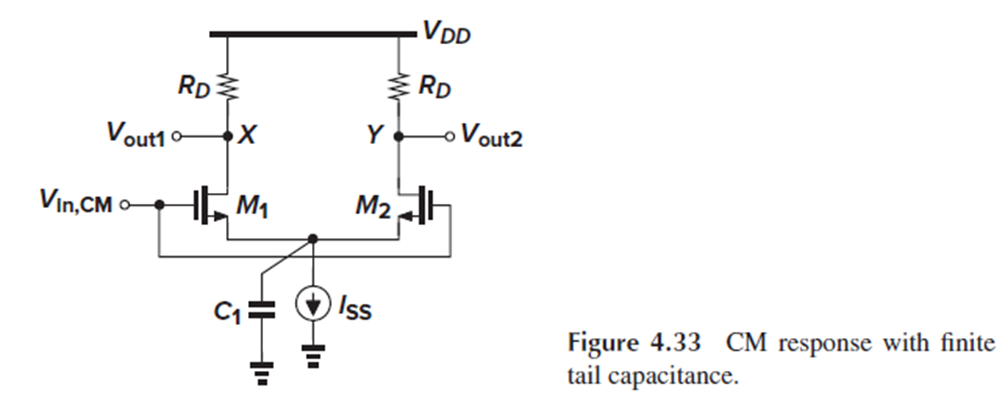

Vin,cm의 주파수가 높아지면, C1으로 흐르는 AC 전류가 증가합니다.

여기서 C1은 tail current source의 parasitic cap과 M1, M2의 source-bulk junction cap이 합쳐진 것입니다.

주파수가 높을수록 C1이 tail current source의 동작에 더 큰 영향을 미치고, common-mode 신호가 differential 신호로 변환되는 정도가 심해집니다.

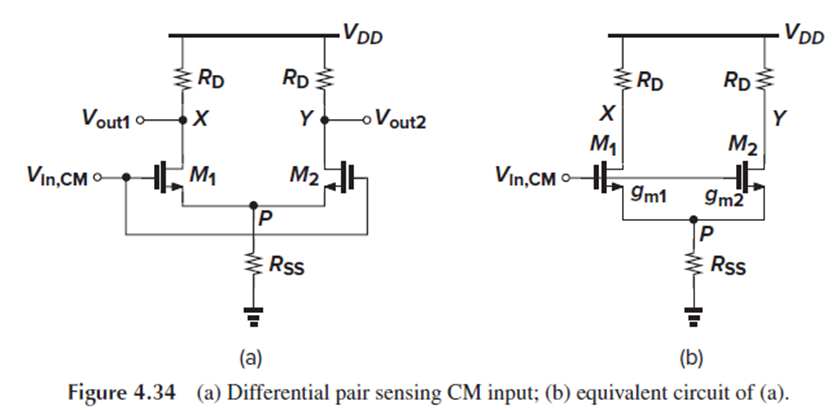

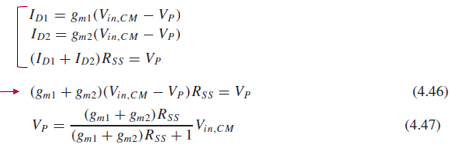

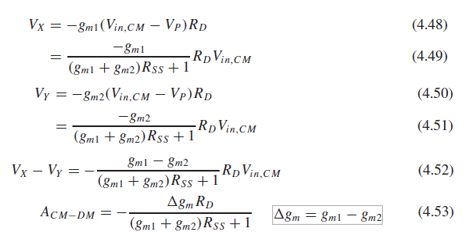

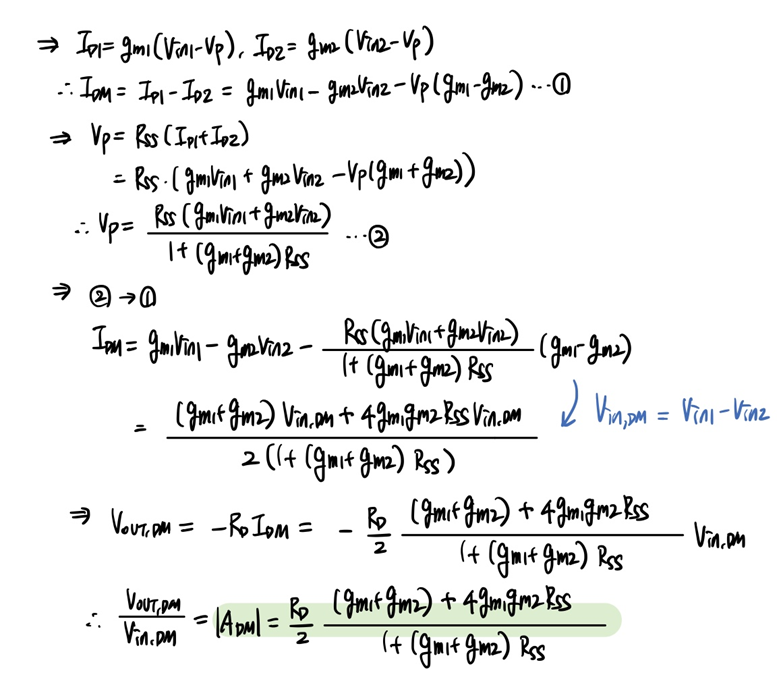

Fig. 4.34(a)의 M1과 M2에 mismatch가 있는 Fig. 4.34(b)의 경우를 봅시다.

M1과 M2의 mismatch로 인해 각 transistor에 흐르는 전류가 달라져서, gm이 각각 gm1, gm2로 다른 값이 됩니다.

(Id1+Id2)Rss = Vp를 (4.46)으로 나타낼 수 있고, 여기서 Vp를 Vin,cm에 대한 식으로 정리하면 (4.47)이 됩니다.

Vx와 Vy를 (4.48)~(4.51)로 쓸 수 있고, 이 둘의 차로부터(4.52) 구한 common-mode to differential-mode conversion은 (4.53)과 같습니다.

Common-Mode Rejection Ratio (CMRR)

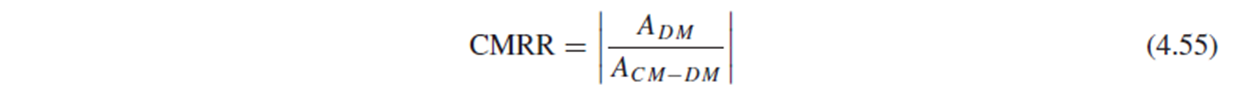

Differential circuit에서 의도한 gain Adm을 원치 않는 gain Acm-dm으로 나눈 값을 common-mode rejection ratio(CMRR)이라고 합니다.

의도한 gain이 크고, 원치 않는 gain이 작으면 CMRR이 크겠죠.

따라서 CMRR은 큰 것이 좋습니다.

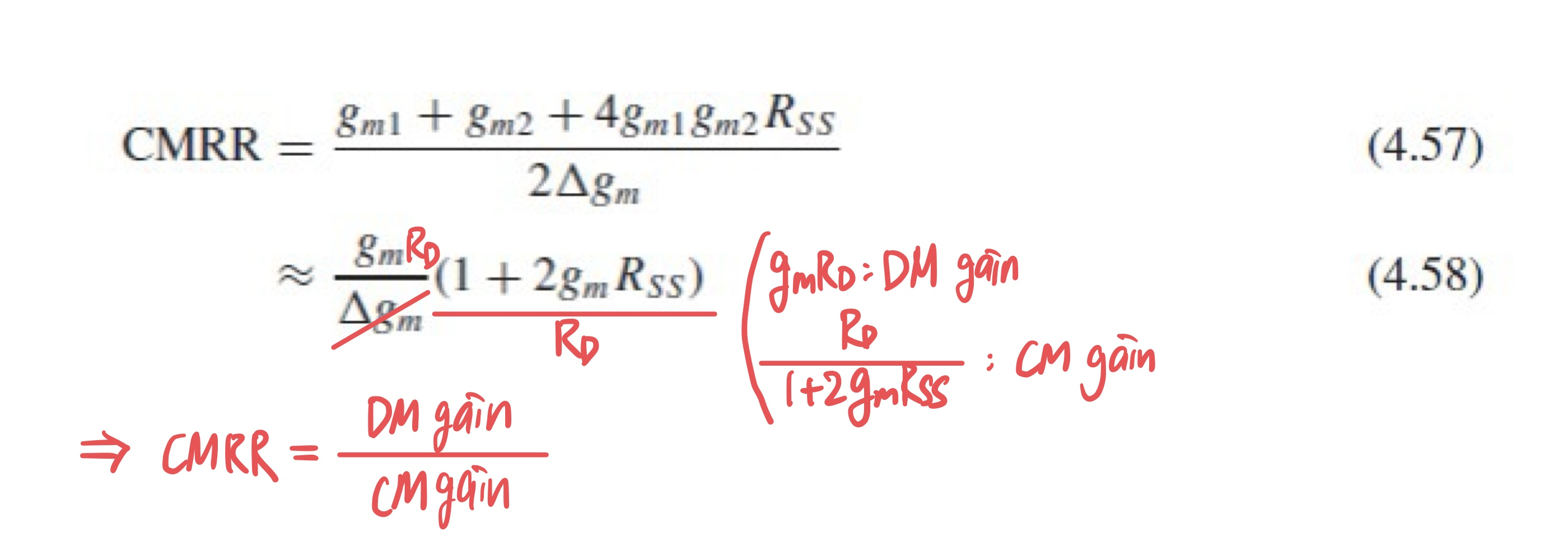

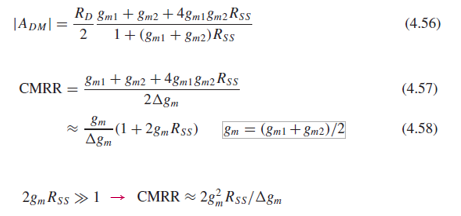

계산 결과 |Adm|이 (4.56)과 같으므로, CMRR은 (4.57)로 구해집니다.

여기서 gm1과 gm2의 평균을 gm이라 하면, (4.58)과 같이 gm에 대한 식으로 CMRR을 나타낼 수 있습니다.

2gmRss가 아주 큰 값이므로, CMRR은 2gm^2Rss/Δgm으로 근사됩니다.

Δgm의 영향을 무시하면, 아래처럼 (4.58)의 CMRR 식을 (DM gain) / (CM gain)으로 볼 수도 있습니다.