참고: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second Edition

Chapter 4 - Differential Amplifiers (pg. 123~128)

4. Differential Amplifiers

4.4. Differential Pair with MOS Loads

Differential Pair with Diode-Connected & Current Source MOS Loads

Differential pair의 load로 저항이 달렸던 이전 포스팅에 이어, load로 MOS가 달린 경우를 보겠습니다.

▼ 이전 포스팅

Degenerated Differential Pair, Common-Mode Rejection Ratio(CMRR) [Razavi][Ch4]

출처: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second EditionChapter 4 - Differential Amplifiers (pg. 116~123)4. Differential Amplifiers4.2. Basic Differential Pair4.2.3. Degenerated Differential Pair Degenerated Differential Pair: Li

soobdal.tistory.com

Fig. 4.37(a)의 load는 PMOS diode입니다.

PMOS diode의 drain에서 본 impedance가 1/gmp || rop이고, NMOS의 drain에서 본 impedance가 ron이므로, small-signal gain은 (4.59)와 같고, (4.60)으로 근사됩니다.

Current source load가 연결된 Fig. 4.37(b)의 small-signal gain은 (4.62)와 같습니다.

뒤에서 diode-connected MOS와 current-source가 병렬된 구조를 load로 사용하는 회로를 볼 거라 각각의 load가 소개된 것입니다.

Diode-connected Load의 문제점: Gain과 Input CM Range 간의 Tradeoff

그런데 Fig. 4.37(a)에서는 diode-connected load가 voltage headroom을 소모해서 gain과 input CM range 간의 tradeoff가 생깁니다.

(3.37)에서 gain을 높이려면, 주어진 Id와 input device의 W/L인 (W/L)1에 대해(즉, 주어진 Vgs1-Vth1에 대해), (3.36)에서 (W/L)p를 감소시켜서 |Vgs2-Vth2|를 증가시켜야 하죠.

이를 Fig. 4.37(a)에 적용하면, gain이 커지려면 |Vgs3-Vth3|(=|Vds3-Vth3|)가 커져야 한다는 말이니까, M3의 drain voltage, 즉 X와 Y의 CM level이 낮아집니다.

해결 방안: Load Device의 Id를 낮춰서 gm 낮추기

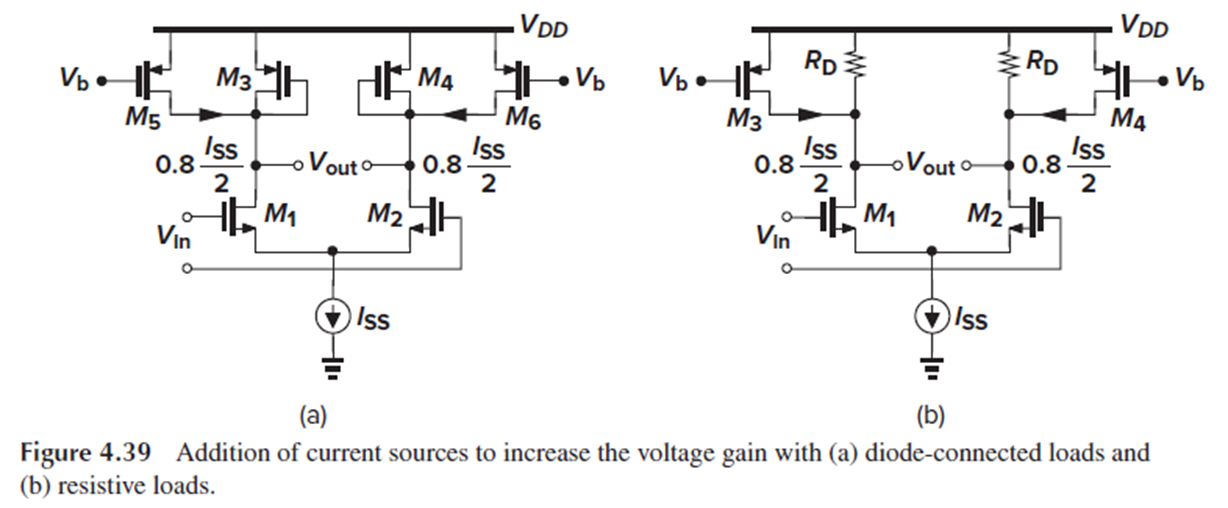

이 문제를 해결하기 위해서, Fig. 4.39(a)처럼, load device M3, M4의 W/L을 낮추는 것이 아니라, Id를 낮춰서 gm을 낮추는 방법을 사용합니다.

보조 current source로 쓰인 M5과 M6가 M1과 M2의 drain current의 80%를 공급해 준다면, M3와 M4에 흐르는 전류가 1/5만큼 줄어듭니다.

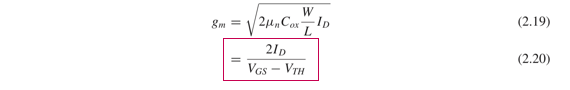

그러면 식 (2.20)에 의해, 주어진 |Vgsp-Vthp|에 대해 gm이 1/5배 감소합니다.

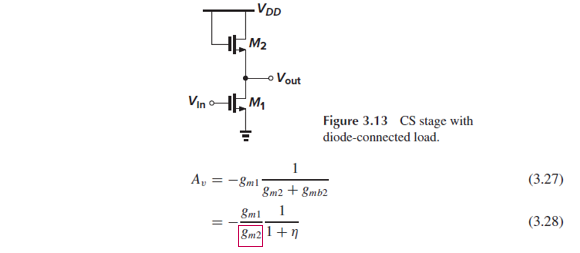

그리고 diode-connected load가 있을 때 gain은 (3.28)과 같은데, 이 경우는 Fig. 3.13에서 gm2가 1/5배 된 것과 같으므로, gain이 PMOS current source가 없을 때보다 5배 증가합니다.

Diode-Connected Load를 Resistor로 바꿔 Output Voltage Swing 늘리기

Diode-connected load의 경우에는 |Vgs| = Vdd-Vout이라서, Vout = Vdd-|Vgs|의 최댓값이 Vdd-|Vth|였습니다.

그런데 resistive load의 경우에는 Vout의 최댓값이 Vdd-|Vgs-Vth|가 돼서, output voltage swing을 늘릴 수 있습니다.

Cascoding으로 Output Impedance(→Gain) 늘리기

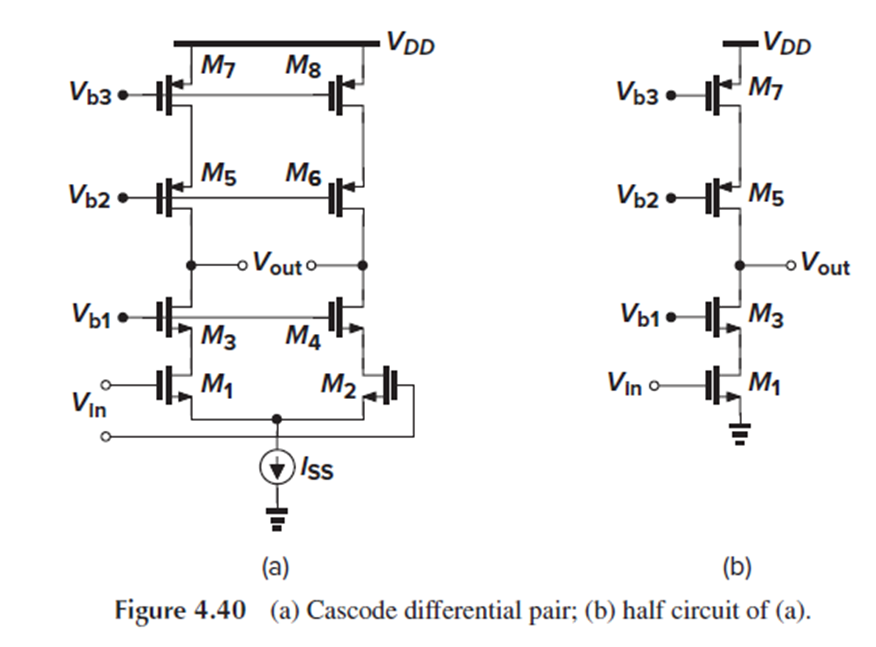

Current-source load를 연결한 differential pair는 small-signal gain이 비교적 낮습니다.

그래서 Fig. 4.40(a)처럼 cascoding을 통해 voltage gain을 높이곤 합니다.

Fig. 4.40(b)의 half-circuit을 그려서 gain을 구하면 (4.65)가 됩니다.

Cascoding을 통해 gain을 늘릴 수 있지만, voltage headroom은 더 소모한다고 합니다. (Ch9: OpAmp에서 자세히 다룸)

4.5. Gilbert Cell

Gilbert cell은 control voltage로 gain을 조절할 수 있는 differential pair로, “variable-gain amplifier”(VGA)의 한 예입니다.

Fig. 4.41(a)는 tail current를 control voltage인 Vcont로 조절해서 gain을 조절하는 것입니다.

Fig. 4.41(b)는 gain을 음수부터 양수까지 조절할 수 있는 회로입니다.

- 두 개의 differential pair가 서로 반대 부호의 gain을 갖고, 전체 Vout은 Vout1+Vout2입니다.

- 여기서 gm은 equilibrium에서 transistor의 transconductance입니다.

- Id1과 Id2를 서로 반대 polarity로 변화시켜서(하나는 증가, 하나는 감소) |Vout1/Vin|, |Vout2/Vin|도 반대 polarity로 변하도록 만드는 것입니다.

- 만약 |Vout1/Vin| > |Vout2/Vin|이면 gain이 음수가 될 것이고, |Vout1/Vin| < |Vout2/Vin|이면 gain이 양수가 될 것입니다.

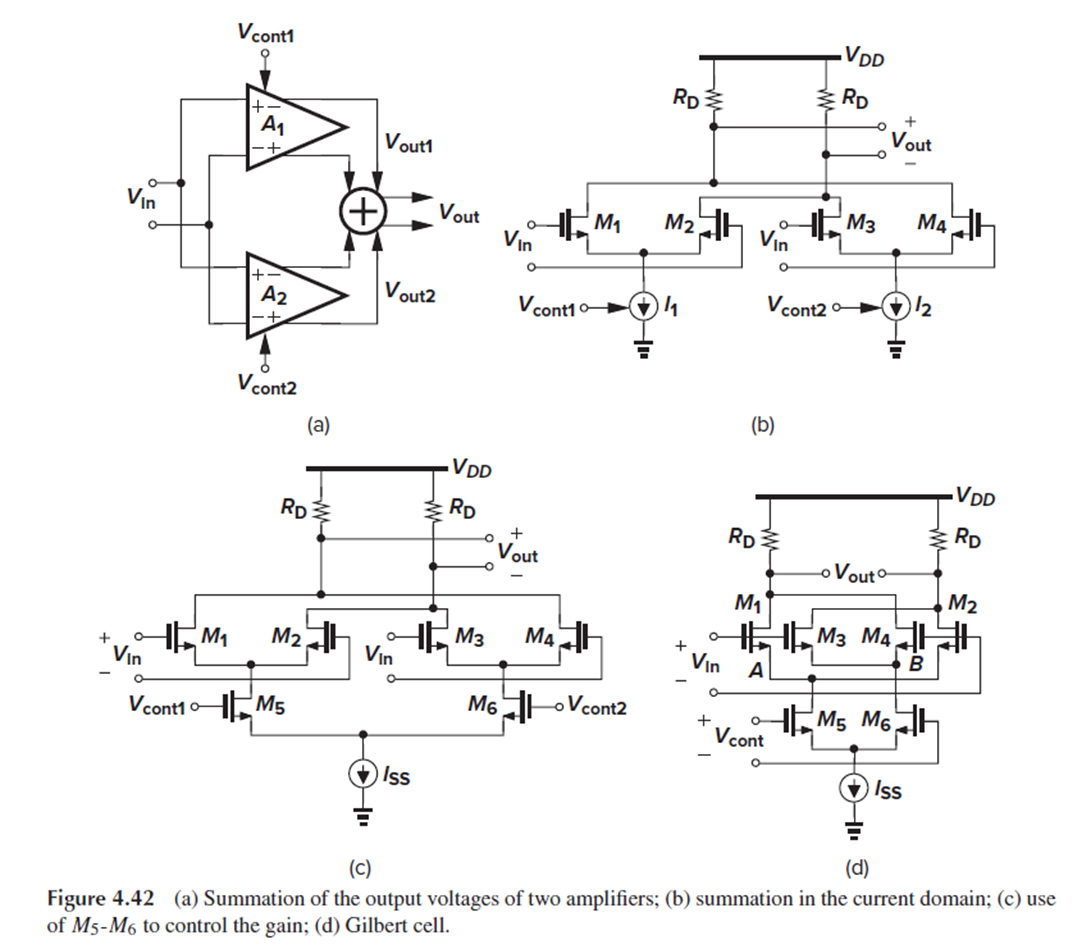

Fig. 4.41(b) 회로에서 Vout1과 Vout2를 더하는 Fig. 4.42(a) 회로를 통해 전체 Vout을 얻을 수 있습니다.

Differential amplifier인 A1과 A2에 differential input Vin이 인가되고 있고, differential output Vout1과 Vout2가 나오고 있습니다.

이 두 output을 더한 Vout이 회로의 최종 output입니다.

Fig. 4.42(b)처럼 drain terminal들끼리 short시켜서 Vout1+Vout2를 수행할 수도 있습니다.

그런데 Fig. 4.42(b) 회로의 I1과 I2가 서로 반대 polarity로 변하게 하기 위해, Fig. 4.42(c)처럼 tail current Iss를 사용합니다.

그러면 M5에 흐르는 I1과 M6에 흐르는 I2가 서로 반대 polarity를 갖겠죠.

Fig. 4.42(c)에서 gate voltage가 Vin+인 것과 Vin-인 것으로 묶어 Fig. 4.42(d)로 단순화해서 그릴 수 있고, Fig. 4.42(d)가 바로 “Gilbert cell”입니다.

보통 M1부터 M4는 모두 동일하고, M5와 M6도 동일하게 설계합니다.

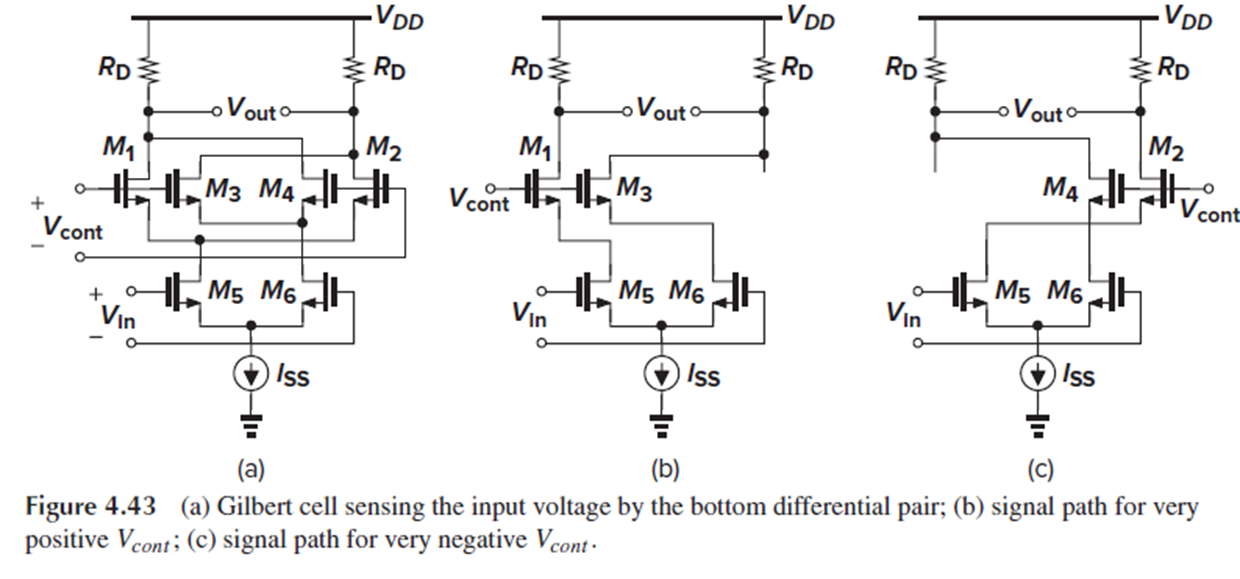

직전에 본 Gilbert cell에서는 Vcont를 M5와 M6에 인가하고, Vin을 M1~M4에 인가했습니다.

그런데 Fig. 4.43(a)에서는 반대로, Vin을 M5와 M6에 인가하고, Vcont를 M1~M4에 인가합니다.

Fig. 4.43(b): 그러면 Vcont가 아주 큰 양수일 때, M1과 M3만 켜져서 Vout이 아래와 같게 됩니다.

Fig. 4.43(c): Vcont가 아주 작은 음수일 때는 M2와 M4만 켜져서 Vout이 아까의 음수 형태가 됩니다.

Vcont=0이면 Vout도 0입니다.

이렇게 Gilbert cell은 Vcont를 조절해서 gain을 음수부터 양수까지 낼 수 있는 회로입니다.