참고: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second Edition

Chapter 5 - Current Mirrors and Biasing Techniques (pg. 160~166)

5. Current Mirrors and Biasing Techniques

5.4. Biasing Techniques

이 단원은 회로에 bias를 인가하는 방법을 설명하며, 아래의 목차로 구성되어 있습니다.

- 5.4.1. CS biasing

- Simple CS stage

- CS stage with current-source load

- Complementary CS stage

- 5.4.2. CG biasing

- 5.4.3. Source follower biasing

- 5.4.4. Differential pair biasing

CS Biasing - Simple CS Stage

Fig. 5.43 설명

- (a): CS stage의 Vin을 biasing하려 합니다.

- (b): Vin과 Vb가 충돌하지 않도록, Vin을 Cb로 coupling시키고 Vb에 크기가 큰 저항인 Rb를 연결합니다.

- 그러면 Vin의 ac 성분과 Vb의 dc 성분이 M1에 전달됩니다.

- 이는 high-pass filter의 구조와 같습니다. fc=1/(2πRbCb)보다 큰 주파수의 신호만 통과시키겠죠.

- 따라서 fc는 Vin의 최소 주파수보다 작도록 설계해야 합니다.

- (c): Vb를 고정된 값으로 인가하는 것이 아니라, diode connected load로 구현합니다.

- Ib의 값은 Id1의 1/10~1/5배로 합니다. Bias network로 인한 전력 소모를 최소화하기 위함입니다. (?)

- (d): RbCb가 커야 하는 application에서는(fc가 작아야 한다면), Rb를 deep triode region에서 동작하는 MOSFET으로 대체할 수 있습니다.

- (2.11)의 Ron 식에 의해, 큰 Rb를 위해서는 Mr의 W/L와 Vov=Vgs-Vth를 작게 하면 됩니다.

- (e)(*): Vov가 작을 때, PVT 변화에도 Mr이 꺼지지 않고, saturation에서 안정적으로 동작하도록 보장해야 합니다.

- Mr이 꺼지지 않고 saturation에서 동작하기 위한 조건은 Vg-Vb < Vth입니다.

- (Mr의 saturation 조건: Vds > Vgs-Vth à Vg-Vd < Vth à Vg-Vb < Vth)

- 작은 Vov = Vgs-Vth(작은 Vg)에 대해 PVT 변화에 의해 Vth가 변해도 Vg-Vb < Vth를 만족하기 위해서는 Vg-Vb ≈ Vth여야 합니다. (?)(Vg-Vb가 엄청 작아야 성립하는거 아님?)

- 이는 diode-connected device로 구현 가능합니다.

- (W/L)c가 크면 Vgs,c ≈ Vth로 Ron,r이 커집니다.

- Strong inversion에서 Ron,r이 (5.58)과 같으므로, 의도하는 대로 Ron,r이 최대가 되려면 (W/L)c가 최대, (W/L)r은 최소여야 합니다.

Fig. 5.44처럼 coupling capacitor를 사용하지 않고, bias voltage를 이전 stage로부터 받는 cascade로 구현해도 될까요?

답은 ‘안 된다‘ 입니다.

이렇게 구현하면 M2의 bias condition이 M1의 bias condition의 영향을 받아, 앞 stage의 PVT variation이 뒤 stage에 증폭되는 문제가 생기기 때문입니다.

CS Biasing - Simple CS Stage

Fig. 5.45 설명

- (a): 저항 대신 current-source load가 있는 CS stage입니다.

- (b): Fig. 5.43의 biasing 방법을 M1과 M2에 적용합니다.

- M1, M2에 흐르는 Id1, Id2는 각각 Ib1, Ib2와 같습니다. M1과 Mb, M2와 M5의 Vgs가 각각 같기 때문입니다.

- 그런데 만약 Id1과 Id2가 같지 않다면, 둘 중 더 작은 전류로 강제로 설정될 것입니다.

- 만약 Id1 > |Id2|라면, Vout의 parasitic cap으로부터 전류를 끌어와 부족한 전류를 충당하므로 Vout이 감소합니다.

- Vout이 감소하면 M1이 triode region에 빠지고, 결국 Id1=|Id2|가 됩니다. 큰 전류가 작은 전류 값에 맞춰진 것이죠.

- (c): 이를 해결하기 위해, M2가 DC에서 diode-connected device이도록 회로를 변경합니다.

- DC에서는 M2에 Id1이 흐르도록 Vgs2가 설정됩니다.

- 고주파에서는 Cg가 M2의 gate를 ground로 short시켜(고정 전압 VDD는 고주파에서 gnd), (5.59)의 small-signal gain이 생깁니다.

- Rg >> ro1||ro2 이도록 하고, 1/(2πRgCg)가 최소 Vin보다 작도록 RgCg 값을 설정합니다.

- 단점은, diode-connected 구조 때문에 Vout이 Vdd-|Vgs2|로 설정된다는 것입니다.

- (d): Rg에 일정한 전류 Ig가 흐르도록 current source를 추가합니다.

- Vn이 충분히 낮으면 M2의 |Vgs|가 충분한 값을 가지는 동시에, Vout은 Vn+IgRg=Vdd-Vgs2+IgRg로 커지는 장점이 있습니다.

두 회로에서 M2는 diode-connected device입니다.

비록 M2의 gate와 drain 사이에 Rg가 있어서 완벽하게 Vg2 = Vd2는 아닐지라도, Rg가 매우 큰 값이라 Vg2 ≈ Vd2입니다.

Fig. 5.45(c)의 경우, Vout은 Vdd - |Vgs2|를 중심으로 최대 전압이 Vdd - |Vgs2-Vth2| (M2의 saturation 조건), 최소 전압이 Vgs1-Vth1입니다(M1의 saturation 조건).

Output voltage swing은 Vdd-|Vgs2|-Vth2부터 Vgs1-Vth1 사이로 제한되지만, 중심 전압으로부터 상향, 하향 swing이 비대칭적입니다.

이는 output voltage swing의 효율을 떨어뜨리는 요인이 되며, peak-to-peak swing은 2[Vdd-|Vgs2|-(Vgs1-Vth1)]입니다.

Fig. 5.45(d)의 경우, 상향 swing은 여전히 Vdd - |Vgs2-Vth2|이고 하향 swing도 여전히 Vgs1-Vth1이나, 중심 전압이 Vdd-|Vgs2|+IgRg입니다.

IgRg가 Vdd/2-|Vgs2|로 설정되면, output swing의 중심이 상향과 하향 swing의 중간 지점인 Vdd/2에 가까워집니다.

이에 따라 상향, 하향 swing이 대칭적으로 조정되고, peak-to-peak swing은 2[Vdd/2 – (Vgs1-Vth1)]로 증가합니다.

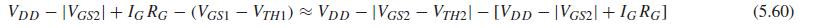

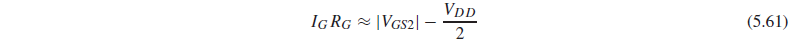

CS Biasing - Complementary CS Stage

- (a): 이 회로는 M1의 drain에 active load인 M2가 연결된 complementary CS stage입니다.

- Vgs1+|Vgs2| = Vdd이므로 이 회로는 PVT에 민감한 특성을 갖습니다.

- Vgs-Vth에서 Vth가 PVT에 따라 변하는데, Vgs1+|Vgs2| = Vdd 조건에 의해 Vgs1, Vgs2의 변화는 제한되어, M1이나 M2가 saturation 조건인 Vds > Vgs-Vth를 만족하지 못하게 될 수 있습니다.

- 또한, M1와 M2에 흐르는 전류가 같지 않다면 두 전류가 서로 싸우게 됩니다.

- (b): M1과 M2의 drain과 gate 사이에 저항 Rf를 연결해 diode-connected 구조를 만듭니다.

- 효과 1: Diode 구조로 인해 M1과 M2의 saturation을 보장할 수 있습니다.

- 효과 2: Id1≠Id2더라도 Id1=|Id2|로 맞춰집니다. Id1 > Id2라면, Vout이 감소해서 Vx도 감소하여, Id1=|Id2|가 됩니다.

- 이 경우, bias를 define하기 어렵습니다.

- (c): Current source I1과 capacitor C1을 추가합니다.

- I1을 추가함으로써 Id1=Id2=I1이도록 합니다.

- C1은 회로의 최소 주파수 𝜔min에서 ground에 short 됩니다.

- Current source I1의 내부 저항이나 기생 저항으로 인한 전압강하가 발생하면, M2의 source degeneration에 의해 gain이 감소합니다.

- C1을 추가하여 M2의 source를 gnd로 short 시킴으로써, source degeneration을 막아 gain을 키울 수 있습니다.

- 이때 C1의 값은 (5.62)를 만족하도록 해야 합니다.

- Source degeneration 저항값을 R1이라 하고, 회로의 최소 주파수를 𝜔min이라 하면, 𝜔min=1/(R1C1)이므로 R1=1/(𝜔minC1)입니다.

- R1 << 1/gm2, 즉, 1/(𝜔minC1)<<1/gm2 이면 source degeneration R1을 무시할 수 있습니다.

- 따라서 이 조건을 만족하도록 C1 값을 설정해야 합니다.

- C1을 추가하면 Vout의 swing 범위가 넓어지는 효과도 있습니다.

- (d): Node X에서의 bias voltage가 Vout을 track해야 하기 때문에, Cin을 연결하여 capacitive coupling시킵니다.

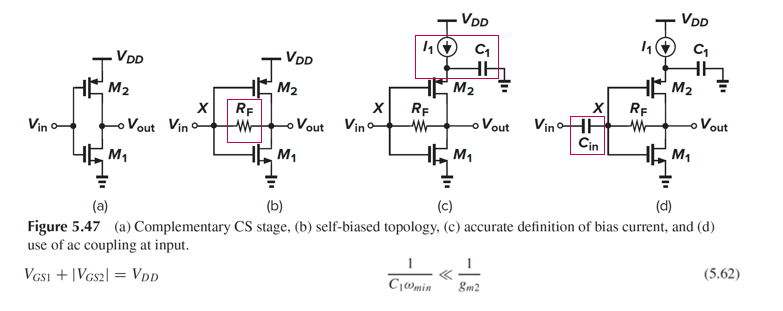

CG Biasing

* CG stage는 source로 input을 받고, output이 drain에 연결된 구조죠.

- (a): M1에 흐르는 I1을 설정하기 위해, current mirror 구조인 오른쪽 branch를 M1의 gate에 연결합니다.

- Current mirror가 제대로 작동하게 하기 위해, M1과 Mb의 Vgs를 같게 하고, W/L을 원하는 비율로 조정합니다.

- 이때, M1과 Mb의 Vgs가 같으려면 Rb/Rs=Id1/Ib여야 합니다.

- 그런데 (a) 회로는 저전력에서 Rs로 인해 attenuation이 생겨, Vin Vx로 잘 전달되지 못한다는 문제가 있습니다.

- Vx/Vin의 식은 (5.63)과 같은데, Rs로 인한 attenuation을 줄이려면 Rs의 크기를 키워야 합니다.

- 그런데 Rs를 키우면 output voltage gain이 줄어듭니다.

- (b): 따라서 Rs를 current source로 대체합니다.

- Channel-length modulation 때문에 Mb에서 M2로의 drain current 복사에 error가 생길 수 있습니다.

- (c): low-voltage cascode를 사용함으로써 이를 해결합니다. (5.2 참고)

- Vds2=Vb-Vgs1, Vdsb=Vb-Vgs3이므로 Vgs1=Vgs3이면 Vds2=Vdsb이도록 할 수 있습니다.

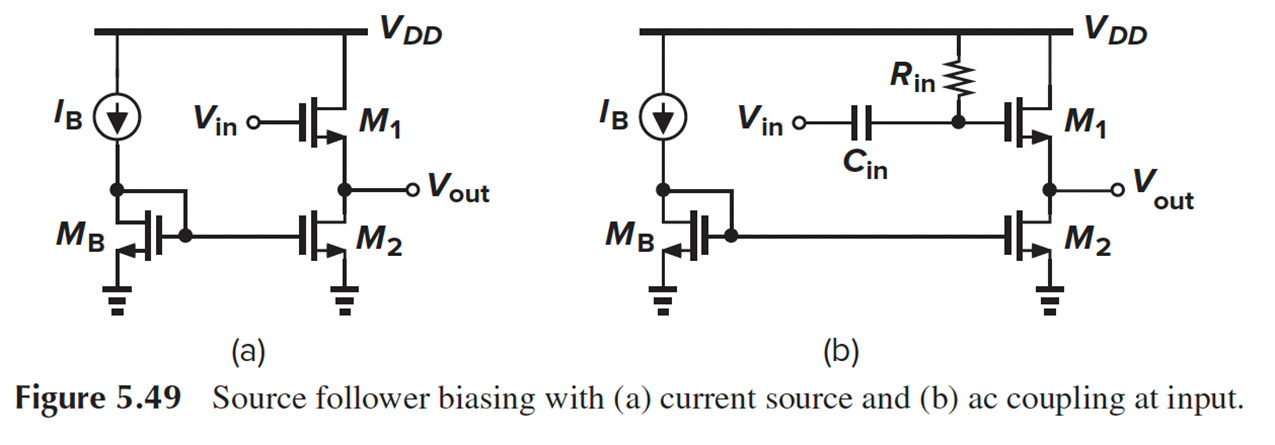

Source Follower Biasing

* Source follower는 input을 gate로 인가하고 output이 drain에 연결된 구조입니다.

- (a): 왼쪽의 bias 회로에 흐르는 Ib가 오른쪽의 M1과 M2에도 흐르게 됩니다.

- (b): Input DC voltage가 크게 변하는 경우에는 Vin을 capacitive coupling 시킵니다.

- Vin의 AC 성분을 가져오고, Rin을 통해 VDD와 연결함으로써 DC bias를 잡아줍니다.

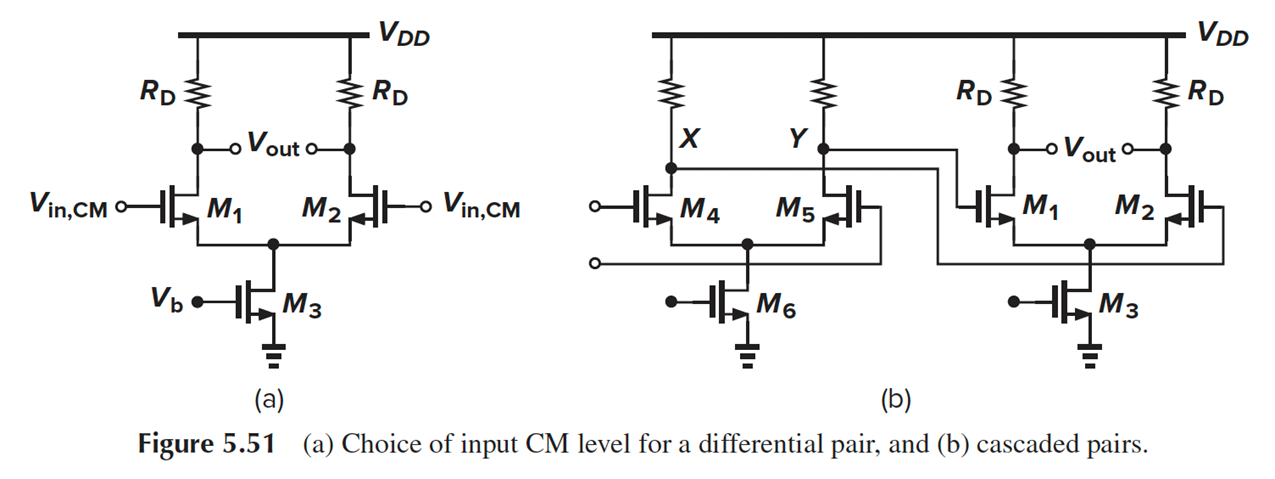

Differential Pair Biasing

Differential pair의 gate voltage를 bias하는 방법입니다.

- (a): Voltage gain과 output swing을 최대로 가져가기 위해, 최저의 input CM level을 선택합니다.

- 이때 Vin,cm = Vgs1,2 + Vds3,min입니다.

- Vds1,2 = (Vgs1,2-Vth1,2) + Vds3,min가 되어 Rd가 최대가 됩니다.

- (b): M1과 M2의 gate voltage를 앞 stage에 의해 결정되도록 cascading한 구조입니다.

- 단점은, 첫 번째 stage의 gain을 늘리기 위해 Vx와 Vy를 2Vov로 설정했다면, 두 번째 stage의 Vin,cm이 매우 작아진다는 점입니다.

- 그래서 capacitive coupling을 사용하고 bias를 따로 잡아줍니다.

- 실제로는, input CM level을 낮지 않게 설계합니다.