참고: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second Edition

Chapter 2 - Basic MOS Device Physics (pg.7~10)

오늘날 Integrated Circuits(IC) 산업에서는 반도체 소자를 이해하는 것이 매우 중요합니다.

특히 디지털 회로설계보다 아날로그 회로설계에서 더 중요한데, 아날로그 회로에서는 트랜지스터가 단순히 switch의 역할을 하는 것이 아니라, 트랜지스터의 second-order effect들이 성능에 직접적인 영향을 미치기 때문입니다.

반도체의 사이즈가 작아짐에 따라 이 효과들이 더욱 중요해졌습니다.

이 단원(Ch2)에서는 MOSFET physics 기초를 다룹니다. 다루는 내용에는 MOS 트랜지스터의 구조, I/V characteristic, second-order effect(body effect, channel-length modulation, subthreshold conduction), MOSFET의 parasitic capacitance, small-signal model, 간단한 SPICE model이 있습니다.

Ch3~14에서 다양한 아날로그 회로를 배우고, Ch17에서 다시 MOS operation를 다룬다고 합니다.

2.1. General Considerations

2.1.1 MOSFET as a Switch

MOSFET의 Symbol

그림은 n-type MOSFET의 symbol입니다. Gate(G), Source(S), Drain(D)의 세 terminal이 있죠.

G를 기준으로 S와 D의 위치가 정해져 있는 것이 아니라, 전압이 높은 쪽이 D, 전압이 낮은 쪽이 S가 됩니다. 이를 S와 D가 interchangable하다고 하며, 따라서 MOSFET은 symmetric한 device입니다.

MOSFET 스위치

MOSFET이 스위치로 동작하는 과정은 이러합니다.

Gate에 걸리는 전압, 즉 Vg가 "high"이면, S와 D가 전기적으로 연결됩니다(on).

반대로, Vg가 "low"이면, S와 D는 연결되지 않습니다(off).

여기서 S와 D의 전기적 연결을 결정하는 Vg의 값을 threshold voltage라고 합니다.

Theshold voltage는 어떻게 결정될까요?

MOSFET이 on, off 상태일 때 S와 D 사이의 resistance은 얼마일까요? 이 저항이 Vs, Vd와 어떤 관계일까요?

S와 D 사이의 전기적 통로를 항상 간단한 resistor로 모델링할 수 있을까요?

Device의 속도를 제한하는 요인에는 어떤 것이 있을까요?

이 질문들에 대한 대답은 트랜지스터의 구조와 원리를 통해 알 수 있습니다.

2.1.2. MOSFET Structure

MOSFET의 구조

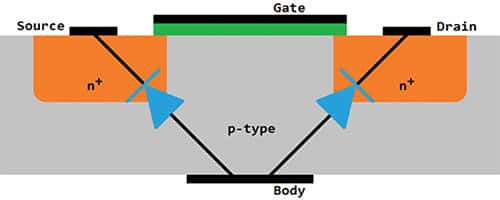

Figure 2.2는 n-type MOS(NMOS)의 모식도입니다.

p-type substrate("bulk", " body"라고도 함) 위에 두 개의 heavily-doped n region(n+)이 source와 drain을 이룹니다.

Heavily-doped(conductive) polysilicon(간단하게 "poly")이 gate로 기능합니다.

얇은 SiO2 층(간단하게 "oxide")이 gate와 substrate를 전기적으로 분리하면서도(insulate), 전기장을 통해 channel을 제어할 수 있도록 합니다.

Doping이란 4족 원소인 Si를 3족 또는 5족 원소로 치환하여, hole 또는 전자를 만드는 것입니다.

- p-doping: Si를 B(붕소), Al(알루미늄), Ga(갈륨)와 같은 3족 원소로 치환하여 hole의 수를 늘립니다.

- n-doping: Si를 P(인), As(비소), Sb(안티모니) 같은 5족 원소로 치환하여 전자의 수를 늘립니다.

Heavily-Doped Source/Drain

여기서 source와 drain이 'heavily'-doped 되는 이유는 크게 두 가지가 있습니다.

첫째, source와 drain을 고농도로 doping해야 channel로의 전자의 공급이 원활해지기 때문입니다.

Gate에 전압이 인가될 때 전자가 쉽게 channel*로 주입되어, transistor가 효과적으로 switching할 수 있다는 뜻입니다.

*channel: source와 drain 사이에 전류가 흐르는 통로

저농도로 doping하면 gate 전압이 인가될 때 depletion이 발생할 수 있습니다.

고농도 doping은 자유 전자의 수를 증가시켜, depletion을 방지하고 강력한 전도성을 유지합니다.

둘째, 고농도로 doping된 source와 drain은 전압 강하를 감소시킵니다.

고농도로 doping하면 transistor 동작 도중 source와 drain 영역에서의 전압 강하가 최소화되어, 가해진 전압 대부분이 transistor 동작을 제어하는 데 사용되고 저항 손실로 낭비되지 않도록 합니다.

Heavily-Doped Gate

Gate가 heavily-doped인 이유는, gate의 전도성을 높이고 전기장 형성을 강화하여, transistor가 더 빠르고 안정적으로 동작할 수 있도록 하기 위해서입니다.

'MOS'에서 'M'은 gate를 의미하지만, gate가 실제로 metal인 것은 아닙니다.

1970년대 이후, metal 대신 heavily-doped polysilicon이 gate의 역할을 하기 시작했는데, 그 이유는 아래와 같습니다.

- 공정 호환성: Polysilicon은 반도체 공정에서 쉽게 사용할 수 있으며, SiO2(oxide)와 잘 결합되기 때문에 제조 공정이 용이합니다.

- 도핑을 통한 전도성 조절: Polysilicon은 doping을 통해 n형 또는 p형으로 전도성을 조절할 수 있습니다. 이를 통해 MOSFET의 특성을 더욱 세밀하게 제어할 수 있습니다.

- 고온 공정 안정성: 금속은 고온에서 변형될 수 있지만, polysilicon은 고온에서도 안정적이어서 반도체 제조 공정에서 유리합니다.

그런데 최근에는 High-k/Metal Gate (HKMG) 기술이 발전하면서 다시 metal gate가 사용되기도 합니다.

Polysilicon gate는 소자 크기가 작아지면서 공핍 효과 등의 문제가 발생했기 때문에, 고성능 transistor에서는 metal gate가 다시 채택된 것입니다.

MOSFET의 Symmetry

다시 한 번, MOSFET 구조는 S와 D에 대해 symmetric합니다.

S는 charge carrier를 제공하는 단, D는 charge carrier를 제공받는 단이라 정의됩니다.

NMOS의 경우, charge carrier가 electron이기 때문에, electron을 제공하는 S가 D보다 낮은 전압을 갖는 것이죠.

L와 Leff

S-D path 방향의 gate dimension을 length, L이라 하며, 이와 수직인 gate dimension을 width, W라고 합니다.

S/D junction은 공정 과정에서 "side-diffuse"하기 때문에 실제 S-D 거리는 L보다 살짝 작다고 합니다.

이를 반영한 길이를 Leff라고 하며, 아래 수식과 같이 정의됩니다.

Leff는 "effective" length, Ldrawn은 total length, L_D는 side diffusion에 의해 줄어든 길이를 나타냅니다.

나중에 더 알아보겠지만, Leff와 gate oxide 두께(tox)가 MOS 회로의 성능에 중요한 영향을 미칩니다.

다른 parameter들을 저하시키지 않으면서 Leff와 tox를 줄이는 것이 MOS 기술 발전에 중요합니다.

Leff와 tox의 typical한 값은 Leff ≒ 10nm, tox ≒ 15A입니다.

앞으로의 설명에는 이 Leff를 L이라 부를 것입니다.

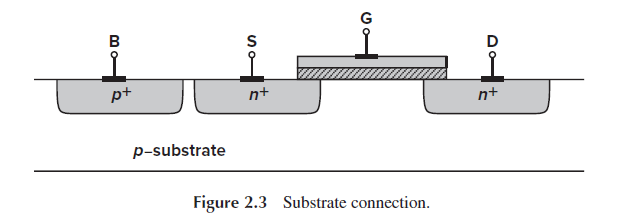

MOSFET의 Substrate

MOSFET의 substrate 전압은 device의 성능을 크게 좌우합니다.

즉, MOSFET의 terminal로 S, G, D 뿐 아니라 substrate도 고려하여야 합니다.

따라서 MOSFET은 4-terminal device입니다.

일반적인 MOS 동작에서, S/D junction diode는 reverse-biased 되어야 합니다.

NMOS를 기준으로 이를 설명하겠습니다.

NMOS에서 S, D는 n-type, substrate는 p-type이죠.

S/D junction이라 함은 S와 D가 각각 substrate와 이루는 n-p junction을 말합니다. (p-n junction과 같은 것인데, 단지 S-substrate, D-substrate가 n-p라서 n-p junction이라 칭했습니다.)

이 S/D junction은 한 방향으로만 전류가 흐르는 diode처럼 작동하는데요.

Forward-biased일 때 전류가 흐르고, reverse biased일 때 전류가 흐르지 않습니다.

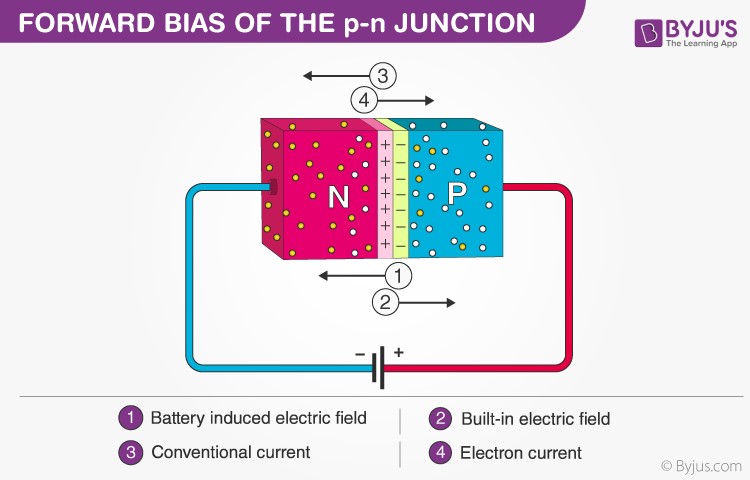

*Forward-biased: p-type이 배터리의 (+)에, n-type이 배터리의 (-)에 연결됨 (Reverse-biased는 그 반대)

Forward-biased일 때는 ①battery induced electric field에 의한 ③conventional current와, ②built-in electric field에 의한 ④electron current가 서로 상쇄되면서 depletion region이 얇아져, 전류가 p-type → n-type로 흐르게 됩니다.

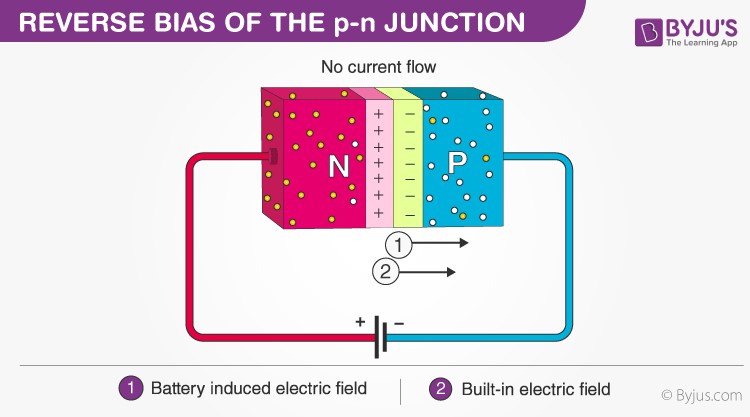

그러나 reverse-biased일 때는 ①battery induced electric field가 ②built-in electric field와 합쳐지면서 더욱 두껍고 resistive한 depletion region이 만들어집니다. 따라서 reverse-biased일 때는 p-n junction에 전류가 흐를 수 없습니다.

다시 MOSFET에서의 n-p junction 얘기로 돌아와서, MOSFET의 S/D와 substrate는 전기적으로 끊겨 있어야 합니다.

전류가 S와 D 사이에만 흐르도록 의도된 소자이기 때문입니다.

substrate와 S/D로 이루어진 p-n junction에 전류가 흐르지 않도록 하기 위해, p-n junction에 reverse-bias를 걸어 줍니다.

즉, substrate를 system에서 가장 negative한 supply에 연결해 주는 것이죠.

(PMOS의 경우, substrate를 system에서 가장 positive한 supply에 연결해 줍니다.)

예를 들어, 0 ~ 1.2V에서 동작하는 회로가 있다면, 그 회로를 이루는 NMOS의 Vsub은 0V, PMOS의 Vsub은 1.2V입니다.

실제로는 NMOS의 substrate에 ohmic p+ region(B)을 만들어 이 효과를 냅니다.

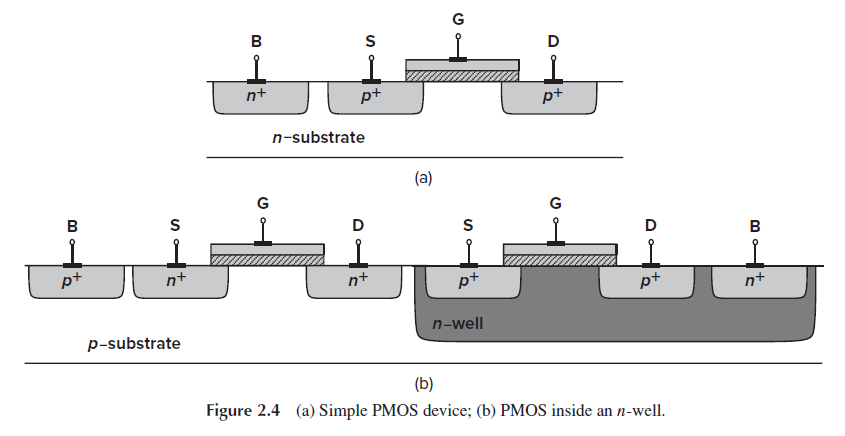

CMOS의 N-Well

회로 설계에 널리 쓰이는 complementary MOS(CMOS) 공정은 NMOS와 PMOS를 동시에 쓰는 기술입니다.

지금까지 살펴본 NMOS의 전하를 모두 반대로 바꾸면 PMOS가 됩니다.

그런데 이 둘을 같은 wafer에 올리기 위해, 둘 중 하나는 "well"이라는 "local substrate"에 놓게 됩니다.

이렇게 하는 것이죠.

- NMOS: p-substrate에 위에서 살펴본 것처럼 생성

- PMOS: p-substrate에 "n-well"을 만들고, 그것을 n-substrate 삼아 PMOS 생성

이 때, n-well의 potential은 S/D junction diode가 모든 조건에서 reverse-biased일 수 있도록 설정해야 합니다.

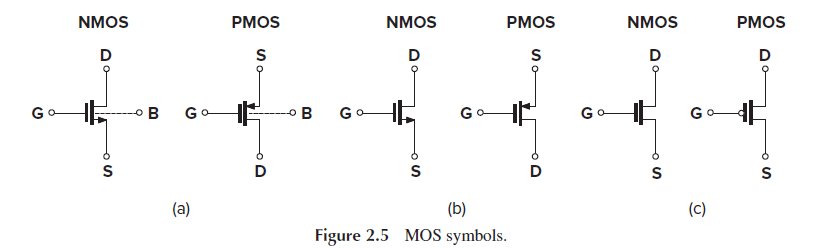

2.1.3. MOS Symbols

NMOS와 PMOS의 대표적인 symbol은 위와 같습니다.

Substrate의 경우 "S" (source)와의 중복을 피하기 위해 "B" (bulk)로 표기합니다.

PMOS의 S는 G보다 높은 전압을 갖기 때문에 편의상 symbol의 위쪽에 위치합니다.

대부분의 회로에서 NMOS와 PMOS의 bulk terminal이 각각 ground와 VDD에 연결되어 있으므로, Figure 2.5(b)처럼 이 연결을 주로 생략하곤 합니다.

디지털 회로에서는 Figure 2.5(c)와 같은 "switch" symbol을 사용하는데, 아날로그 회로에서는 S, D가 구분되는 Figure 2.5(b)를 선호합니다.

'CMOS IC Design' 카테고리의 다른 글

| MOSFET Second-Order Effects(2) - Channel Length Modulation [Razavi][Ch2] (0) | 2024.10.06 |

|---|---|

| MOSFET Second-Order Effects(1) - Body Effect [Razavi][Ch2] (1) | 2024.10.06 |

| MOSFET의 I/V 특성(2) - Transconductance(gm) [Razavi][Ch2] (1) | 2024.10.05 |

| MOSFET의 I/V 특성(1) - Triode, Saturation, Pinch-off, Id 수식 [Razavi][Ch2] (0) | 2024.10.04 |

| MOSFET의 문턱 전압(Threshold Voltage, Vth) [Razavi][Ch2] (0) | 2024.10.04 |