참고: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second Edition

Chapter 2 - Basic MOS Device Physics (pg.23~24)

2.3. Second-Order Effects

이 단원 전까지는 MOS 구조를 쉽게 이해하기 위해, 실제 아날로그 회로와는 맞지 않는 여러 가지 가정을 붙였습니다.

이 단원에서는 실제 회로 동작에 가깝고, 이후의 회로 분석에 매우 중요한 4개의 second-order effect를 알아볼 것입니다.

바로 body effect, channel-length modulation, subthreshold conduction, punch-through입니다.

이 포스팅에서는 이 중 channel-length modulation에 대해 알아보겠습니다.

다른 second-order effect에 대한 내용은 아래 링크들에 정리되어 있습니다.

2024.10.06 - [CMOS IC Design] - MOSFET Second-Order Effects(1) - Body Effect [Razavi][Ch2]

MOSFET Second-Order Effects(1) - Body Effect [Razavi][Ch2]

출처: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second EditionChapter 2 - Basic MOS Device Physics (pg.20~22)2.3. Second-Order Effects이 단원 전까지는 MOS 구조를 쉽게 이해하기 위해, 실제 아날로그 회로와는 맞

soobdal.tistory.com

MOSFET Second-Order Effects(3) - Subthreshold Conduction [Razavi][Ch2]

출처: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second EditionChapter 2 - Basic MOS Device Physics (pg.24~26)2.3. Second-Order Effects이 단원 전까지는 MOS 구조를 쉽게 이해하기 위해, 실제 아날로그 회로와는 맞

soobdal.tistory.com

MOSFET Second-Order Effects(4) - Voltage Limatations, Punch-Through [Razavi][Ch2]

출처: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second EditionChapter 2 - Basic MOS Device Physics (pg.26)2.3. Second-Order Effects이 단원 전까지는 MOS 구조를 쉽게 이해하기 위해, 실제 아날로그 회로와는 맞지

soobdal.tistory.com

Channel Length Modulation

Sec. 2.2에서 channel pinch-off 개념을 설명하면서, Vds가 Vgs - Vth를 넘으면 pinch-off가 발생해, NMOS에 일정한 Id가 흐르는 saturation이 된다고 했었죠.

해당 내용은 아래 링크에서 확인하실 수 있습니다.

MOSFET의 I/V 특성(1) - Triode, Saturation, Pinch-off, Id 수식 [Razavi][Ch2]

출처: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second EditionChapter 2 - Basic MOS Device Physics (pg.12~19)2.2 MOS I/V Characteristics2.2.2. Derivation of I/V CharacteristicsMOSFET의 drain current와 terminal voltage(Vg, Vd, Vs, Vb)의

soobdal.tistory.com

Sec. 2.2에서는 saturation에서의 Id가 수식 2.13과 같이 Vds에 무관한 효과라고 했었습니다.

그런데 실제로는 Vds가 계속 증가하여 gate와 drain의 전압차가 감소하면, channel의 실제 길이가 감소한다고 합니다.

수식 2.13에서 channel의 실제 길이 L'이 실은 Vds의 함수라는 것이죠.

이 효과를 "channel-length modulation"이라고 합니다.

Channel-length modulation에 의해 saturation에서 Id가 증가하는 효과가 나타나는데요, 아래 과정을 통해 살펴봅시다.

L' = L - △L로 표현하면, 아래와 같은 과정을 거쳐 1/L' ≒ (1 + △L/L) / L이 됩니다.

△L/L과 Vds 간에 '△L/L = λVds'와 같은 first-order relationship이 있다고 가정하고 이를 수식 2.13에 대입하면,

saturation에서 channel-length modulation을 고려한 drain current Id는 수식 2.27과 같습니다.

여기서 λ는 "channel-length modulation coefficient"입니다.

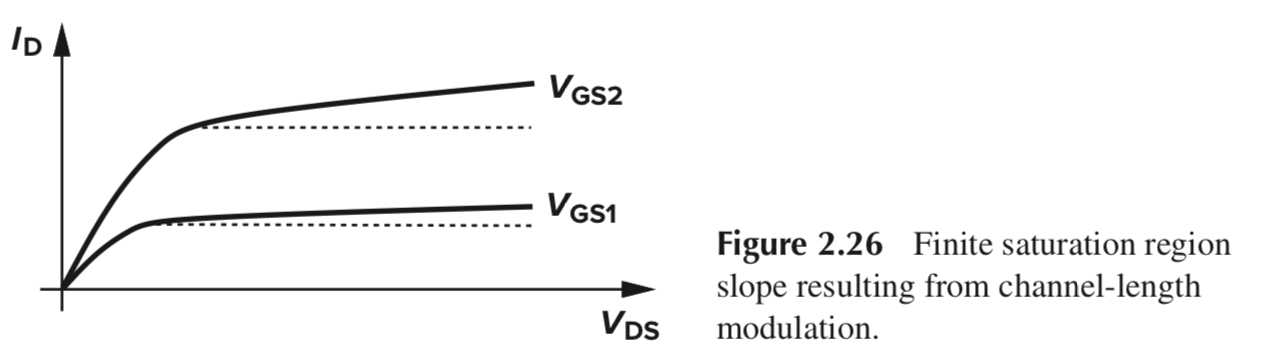

추가된 (1 + λVds) term으로 인해, Id / Vds 그래프의 saturation region이 일정한 값이 아닌, Vds가 증가함에 따라 Id가 증가하는 꼴로 나타납니다. (Figure 2.26)

D와 S 사이의 current source가 nonideal하다고도 해석할 수 있죠.

λ는 Vds의 변화에 따른 '상대적' channel 길이 변화를 나타냅니다.

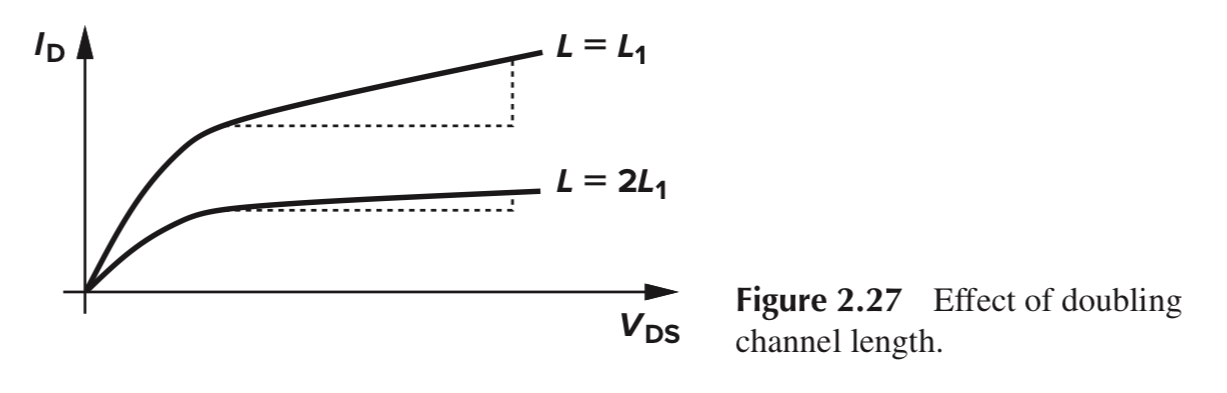

따라서 short channel에서는 λ가 커져 channel-length modulation이 크게 나타납니다.

Figure 2.27에서 보듯, channel 길이 L이 2배 더 짧은 L = L1 case에서 saturation region의 Id가 Vds와 함께 증가하는 channel-length modulation이 더 심하게 나타납니다.

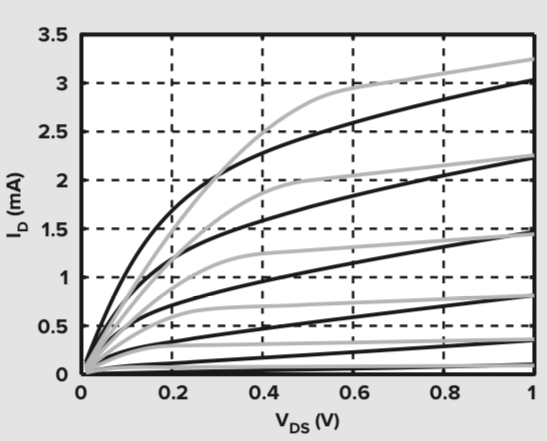

아래 그림을 보면, W/L = 5μm/40nm인 NMOS의 ideal한 Id / Vds 곡선(검은색)과 실제 NMOS의 Id / Vds 곡선(회색)에 큰 차이가 있습니다. (Vgs = 0.3V ~ 0.8V)

Nanometer 단위로 설계되는 오늘날 transistor에서, channel-length modulation에 의해 설계에 어려움이 생기는 이유입니다.

Triode Region에도 channel-length modulation이 있을까?

정답은 No 입니다.

Triode region에는 channel이 source부터 drain까지 연속적으로 존재하기 때문에, pinch-off가 나타나지 않습니다.

따라서, Vds가 channel의 길이에 영향을 미치지 않습니다.

Channel-Length Modulation을 반영한 gm

이전 포스팅에서 gm의 수식을 아래와 같이 구했습니다.

2024.10.05 - [CMOS IC Design] - MOSFET의 I/V 특성(2) - Transconductance(gm) [Razavi][Ch2]

MOSFET의 I/V 특성(2) - Transconductance(gm) [Razavi][Ch2]

출처: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second EditionChapter 2 - Basic MOS Device Physics (pg.19~20)2.2.3 MOS TransconductanceTransconductance, gmSaturation에서 동작하는 MOSFET은 overdrive voltage(Vov)가 인가되면 전

soobdal.tistory.com

여기에 channel-length modulation을 반영하면 아래와 같습니다.

Channel-Length Modulation은 오차로 간주

Vds에 따라 Id가 변한다니, 회로 설계 시에 Vgs - Vth 대신 Vds를 바꿔가며 Id를 조절해도 되는 것 아닌지 생각하실 수도 있는데요.

그럴 수는 없습니다.

Id에 미치는 영향은 Vds보다 Vgs - Vth가 훨씬 더 크기 때문에, Vgs - Vth를 항상 current-defining parameter로 간주합니다.

Vds가 Id에 미치는 영향, 즉 channel-length modulation은 대부분 error로 간주되며, Chapter 5에서 다루게 됩니다.