참고: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second Edition

Chapter 2 - Basic MOS Device Physics (pg.12~19)

2.2 MOS I/V Characteristics

2.2.2. Derivation of I/V Characteristics

MOSFET의 drain current와 terminal voltage(Vg, Vd, Vs, Vb)의 관계를 알아보기 위해, 두 가지 관찰을 해 봅시다.

첫 번째 관찰

먼저, 전류 I가 흐르는 반도체 bar가 있다고 생각하는 겁니다.

만약 전류 방향으로 이동하는 charge density가 Qd[C/m]이고, charge의 속도가 v[m/s]라면, I는 아래와 같은 수식으로 표현됩니다.

이를 이해하기 위해, 단위 시간 동안 bar의 단면을 통과하는 총 charge를 측정해 봅시다.

1초 동안 각 charge는 bar를 따라 v미터를 이동할 것인데, charge density가 미터 당 Qd 쿨롱이므로, v미터 내의 총 charge는 Qd * v가 되겠죠.

두 번째 관찰

Figure 2.10(a)처럼, Source와 Drain이 ground에 연결되어 있는 NMOS가 있습니다.

Inversion layer(channel)에서의 charge density는 어떤 값일까요?

(Inversion이 'Vgs = Vth'에서 즉시 발생한다고 가정합니다.)

Inversion charge density Qd는 gate-oxide capacitance에 의해 발생하므로, Vgs와 Vth의 차이, 즉 'Vgs - Vth'에 의해 발생한다고 할 수 있습니다.

'Q = CV' 공식을 적용하여 수식으로는 아래와 같이 나타낼 수 있습니다.

여기서 W * C_ox는 channel의 단위 길이 당 capacitance를 나타냅니다.

이제 Figure 2.10(b)에서처럼, Vd > 0인 NMOS를 가정해 봅시다.

Channel 내 위치 x가 0부터 L까지 증가하면서, 위치 x에서의 전압 V(x)는 0부터 Vd까지 증가하며, gate와 channel 사이의 local 전압차는 Vg(source 근처)부터 Vg - Vd(drain 근처)까지 변화합니다.

위치 x에서의 charge density Qd(x)는 단위 길이 당 W * C_ox의 capacitance를 갖는 gate-oxide capacitor에 걸리는 전압에 따라 달라집니다.

● x = 0 → V(x) = V(0) = 0 → gate-oxide capacitor에 걸리는 전압 = (Vgs - 0 - Vth)

● x = L → V(x) = V(L) = Vd → gate-oxide capacitor에 걸리는 전압 = (Vgs - Vd - Vth)

따라서, channel을 따라 위치 x의 charge density Qd(x)는 아래와 같습니다.

위에서 도출한 I = Qd * v에 의해, drain current는 아래와 같이 나타납니다.

(-) 부호는 (-)인 Qd로부터 Id를 (+)로 나타내기 위해 붙었습니다.

반도체에서 channel 내 charge carrier의 이동 속도 v = μE (μ: charge carrier의 mobility, E: electric field)

E(x) = - dV/dx이고, 전자의 mobility를 μ_n이라 표기하면,

이 되고, 여기서 V(0) = 0, V(L) = Vds의 boundary condition이 있습니다.

양변을 적분하면 아래와 같고,

channel에서 Id 값은 일정하고, μ_n 과 Vth가 x, Vg, Vd와 independent하다고 가정하면(Ch17에서 더 다룰 것),

가 됩니다. L은 effective channel length, Leff입니다.

MOSFET의 I/V 특성 - Triode Region

Id를 y, Vds를 x로 생각하면, Id는 Vds에 대한 이차함수가 됩니다.

Figure 2.11은 Vgs에 따른 Id/Vds 그래프를 그린 것입니다.

Peak current는 Vds = Vgs - Vth에서

가 됩니다. 이 'Vgs - Vth' 값을 "overdrive voltage"라고 하고, W/L을 "aspect ratio"라고 합니다.

Vds ≤ Vgs - Vth이면, device가 "triode region"에서 작동한다고 합니다.

즉, triode region에서의 drain current는 위의 수식 2.8과 같다는 것입니다. 해당 수식을 아래에 다시 붙입니다.

두 관찰을 통해, Id가 공정에 따라 결정되는 μ_n과 C_ox, 설계자가 조절할 수 있는 W와 L, Vgs와 Vth에 의해 변한다는 것을 알 수 있었습니다.

수식 2.8에서, Vds ≪ 2(Vgs - Vth)이면

로, Id가 Vds에 linear합니다.

수식 2.10으로부터 R_on = Vds / Id를 구할 수 있으며, Vgs가 일정하다면 R_on도 constant합니다.

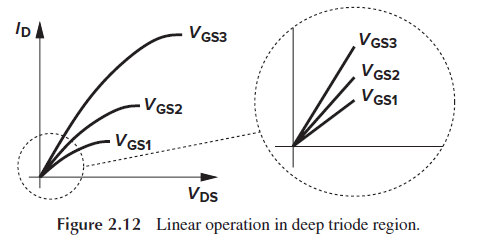

Figure 2.12의 MOSFET I/V curve를 보면, 낮은 Vds에서 그래프가 linear하게 나타납니다.

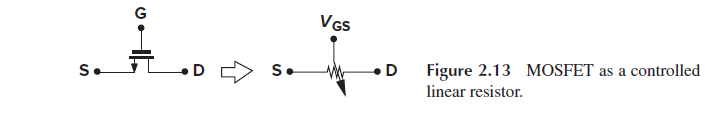

따라서, MOSFET은 Vds ≪ 2(Vgs - Vth)일 때, 다른 말로는 deep triode region에 있을 때, resistor로 작동할 수 있습니다. (Figure 2.13)

수식 2.11에 의해, overdrive voltage Vgs - Vth를 조절하여 resistance 값을 조절할 수 있습니다.

Controllable resistor로써 동작하는 MOSFET은 voltage-controlled resistor나 switch처럼 아날로그 회로에서 중요한 역할을 합니다.

MOSFET의 I/V 특성 - Saturation Region

사실, 수식에 기반해 그린 Figure 2.11의 그래프는 Vds > Vgs - Vth인 구간에서 실제 MOSFET의 동작과 차이가 있습니다.

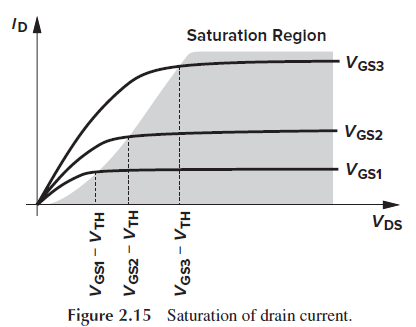

실제로는 Vds > Vgs - Vth일 때, 전류가 포물선을 그리며 작아지는 것이 아니라, Figure 2.15에서 볼 수 있듯 거의 일정한 값을 유지합니다.

Id가 거의 일정하게 유지될 때, device가 "saturation region"에 있다고 합니다.

Saturation region이 나타나는 이유는 곧이어 살펴볼 "pinch-off" 때문입니다.

Pinch-off

위에서도 등장했던 수식 2.4를 다시 보면, inversion layer charge의 local density인 Qd[C/m] 는 'Vgs - V(x) - Vth'에 비례합니다.

V(x)가 Vgs - Vth보다 살짝 커지면, Qd(x) ≥ 0이 되기 시작한다는 것을 수식에서 관찰할 수 있습니다.

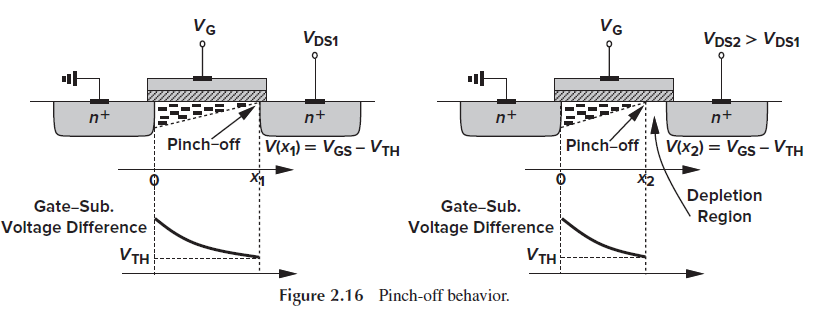

Figure 2.16의 왼쪽 그림은 Vds가 Vgs - Vth보다 살짝 큰 값을 가진 상태입니다.

Channel이 형성되려면 Vds ≥ Vgs - Vth여야 하죠.

Vds가 Vgs - Vth보다 살짝 큰 값을 가진다는 것은, channel이 막 형성된 상태라는 겁니다.

Drain과 아주 가까운 channel의 지점 x1에서 V(x1) = Vgs - Vth, Qd(x1) = 0이겠죠.

즉, inversion layer가 x ≤ L에서 끊기게 되며, 이렇게 channel이 끊기는 것을 channel이 "pinch off" 됐다고 합니다.

그렇다면 Vds가 Vgs - Vth를 넘어 계속 커지면 어떻게 될까요?

Figure 2.16의 오른쪽 그림이 바로 그 상황입니다.

Vds가 계속 커지면, Qd(x2) = 0이 되는 지점 x2, 즉 pinch-off point가 source 쪽으로 밀려나게 됩니다.

Channel이 끊기는 pinch-off point로부터 drain까지는 depletion region이 되겠죠.

Drain과 source의 전압차가 커지면서 source가 전자를 더 세게 끌어당겨서 그렇다고 이해하면 편합니다.

MOSFET에서 'Vds ≥ Vgs-Vth'로 pinch-off 되었을 때, 전자가 pinch-off point에서 멈추어 MOSFET에 전류가 흐르지 않는 것 아니냐고 생각할 수도 있는데요, 아닙니다.

전자가 pinch-off point에 다가갈수록, 즉, Qd → 0이 될 때, 전자의 속도는 크게 증가합니다.

'I = Qd * v (위의 수식 2.2)'로부터 'v = I / Qd'이기 때문이죠.

Pinch-off point를 지나며 속도가 크게 증가한 전자는, drain junction 근처의 depletion region을 빠르게 통과하여(shoot through) drain terminal에 도착합니다.

MOSFET Saturation Region의 Drain Current(Id)

위에서 triode region의 drain current Id 수식을 아래와 같이 구했습니다.

수식 2.7로 돌아가, 이번엔 saturation region의 drain current를 유도해 보겠습니다.

Qd는 'mobile'한 charge의 density를 뜻하므로, saturation region의 Id를 구할 때 왼쪽 integral의 적분 구간 x = 0 ~ L를 그대로 쓰지 않습니다.

Mobile한 charge는 x = 0 ~ L'에 존재한다고 가정합시다. 여기서 L'은 Figure 2.16의 x2과 같습니다.

따라서 왼쪽 integral의 적분 구간을 x = 0 ~ L'로 바꿔 줍니다.

오른쪽 integral의 적분 구간은 V = 0 ~ Vgs - Vth가 되겠죠.

수식 2.7에서 양변 적분구간을 바꾸어 적분하면 아래와 같이 됩니다.

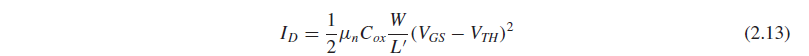

이 수식을 통해, saturation region에서는 Id가 Vds에 무관하다는 것을 알 수 있습니다.

Figure 2.15의 Vgs - Vth를 넘는 Vds 구간에서, 왜 Id가 일정한 건지 이제 이해할 수 있죠.

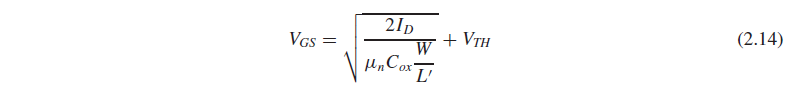

Id를 알고 있다면, 아래 수식을 통해 Vgs를 구할 수도 있습니다.

(그러나 실제로는, MOSFET의 second-order effect 중 하나인 channel length modulation에 의해, Id와 Vds가 무관하지 않습니다. L'이 Vds에 대한 함수이기 때문입니다. 해당 내용은 아래 링크에서 확인할 수 있습니다.)

[Razavi][Ch2] MOSFET Second-Order Effects(2) - Channel Length Modulation

출처: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second EditionChapter 2 - Basic MOS Device Physics (pg.23~24)2.3. Second-Order Effects이 단원 전까지는 MOS 구조를 쉽게 이해하기 위해, 실제 아날로그 회로와는 맞

soobdal.tistory.com

Voltage Headroom과 Vd,sat 값 결정의 중요성

많은 아날로그 회로에서는 MOSFET이 saturation에서 동작하도록 설계합니다.

'Vds ≥ Vgs-Vth = overdrive voltage'여야 한다는 뜻입니다.

그래서 어떤 책에서는 'Vd,sat = Vgs - Vth'라고 쓰기도 합니다.

Vd,sat은 MOSFET이 saturation에서 동작하기 위한 최소 Vds라는 거죠.

Vd,sat, overdrive voltage(Vov), Vgs - Vth가 다 같은 말입니다.

Vds ≥ Vd,sat을 만족하는 게 왜 그렇게 중요하냐면, 만약 회로에서 gate와 drain의 signal swing이 Vds를 Vgs - Vth보다 작게 만든다면 의도하지 않은 효과가 나타날 수 있기 때문입니다.

따라서, signal swing에도 회로가 정상 동작하도록 voltage "headroom"을 둘 수 있게 Vd,sat 값을 결정해야 합니다.

Vd,sat이 크면 클수록, signal swing을 위한 headroom은 작아집니다.

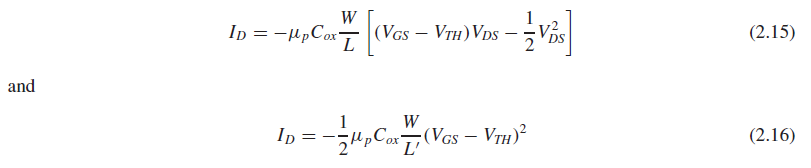

PMOS의 Drain Current(Id)

위에서는 NMOS의 drain current 수식을 알아봤습니다.

PMOS의 경우, triode region과 saturation region에서의 수식이 각각 아래와 같습니다.

Id가 NMOS 기준으로 D → S로 흐른다고 생각하기 때문에, S → D로 흐르는 PMOS의 Id에는 (-) 부호가 붙습니다.

'On' 상태인 PMOS의 Vgs, Vds, Vth, Vgs - Vth는 모두 (-)입니다.

대개 PMOS의 S가 VDD에 연결되어 있으니까요.

PMOS의 charge carrier인 hole의 mobility가 NMOS의 charge carrier인 전자의 mobility의 1/2배인 관계로, PMOS device는 낮은 "current drive" capability를 갖습니다.

Large-Signal Model과 Small-Signal Model

위의 NMOS, PMOS의 Id 수식들(수식 2.8, 2.13, 2.15, 2.16)은 MOSFET의 "large-signal" behavior를 나타냅니다.

G, S, D에 인가된 임의의 전압들로부터 Id를 알아낼 수 있죠(device가 켜져있을 때만).

그런데 이러한 nonlinear한 수식들로 분석하는 것이 복잡하기 때문에, linear approximation을 사용하곤 합니다.

이를 "small-signal" model이라고 하며, Sec.2.4.3에서 자세하게 다룹니다.

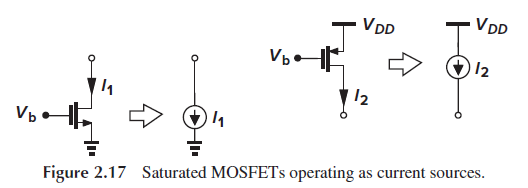

Current Source로서의 MOSFET

L이 constant하다고 가정하면, saturated MOSFET은 current source로 사용될 수 있습니다. (Figure 2.17)

Saturated MOSFET의 drain과 source 사이에 일정한 전류가 흐르기 때문입니다.

NMOS current source는 전류를 ground로 보내고, PMOS current source는 VDD로부터 전류를 끌어옵니다.

NMOS의 drain, PMOS의 drain은 "floating" 상태인 것이죠.

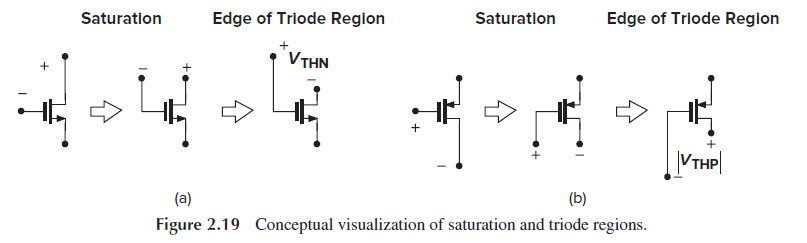

Saturation과 Triode Region을 나타내는 Symbol

MOSFET에서, 특히 PMOS에서, saturation과 triode region의 구분이 헷갈릴 수 있습니다.

Channel의 pinch-off는 Vg와 Vd의 차이가 inversion layer를 만들기에 충분하지 않을 때 발생한다고 했었습니다.

Figure 2.19(a)는 NMOS의 Vg - Vd가 Vthn보다 낮아질 때, pinch-off가 발생한다는 것을 나타냅니다.

PMOS도 같은 방식으로, Figure 2.19(b)는 PMOS의 Vd - Vg가 충분히 크지 않으면(< |Vthp|) saturated임을 나타냅니다.

이 view는 source 전압에 대한 정보를 요구하지 않습니다.

이 말은, 어떤 terminal이 drain으로 작동하는지 알아야 한다는 뜻입니다.

NMOS(PMOS)에서, drain은 source보다 높은(낮은) 전압을 가진 terminal로 정의됩니다.

'CMOS IC Design' 카테고리의 다른 글

| MOSFET Second-Order Effects(2) - Channel Length Modulation [Razavi][Ch2] (0) | 2024.10.06 |

|---|---|

| MOSFET Second-Order Effects(1) - Body Effect [Razavi][Ch2] (1) | 2024.10.06 |

| MOSFET의 I/V 특성(2) - Transconductance(gm) [Razavi][Ch2] (1) | 2024.10.05 |

| MOSFET의 문턱 전압(Threshold Voltage, Vth) [Razavi][Ch2] (0) | 2024.10.04 |

| MOSFET의 구조(Gate, Drain, Source, Body) 및 symbol[Razavi][Ch2] (0) | 2024.10.04 |