참고: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second Edition

Chapter 2 - Basic MOS Device Physics (pg.26~27)

2.4. MOS Device Models

2.4.1. MOS Device Layout

MOSFET Layout

이 단원에서는 MOSFET의 layout에 대해 간단히 설명하며, 더 심화된 내용은 Chapter 18, 19에서 설명합니다.

MOSFET의 layout은 ① 요구되는 전기적 특성, ② 공정의 "design rule"에 따라 결정됩니다.

예를 들어, ① transconductance나 다른 circuit parameter를 맞추기 위한 W/L과, ② L의 최소 길이를 지켜 layout을 그립니다.

Gate, source, drain area 모두 제대로 정의되어야 합니다.

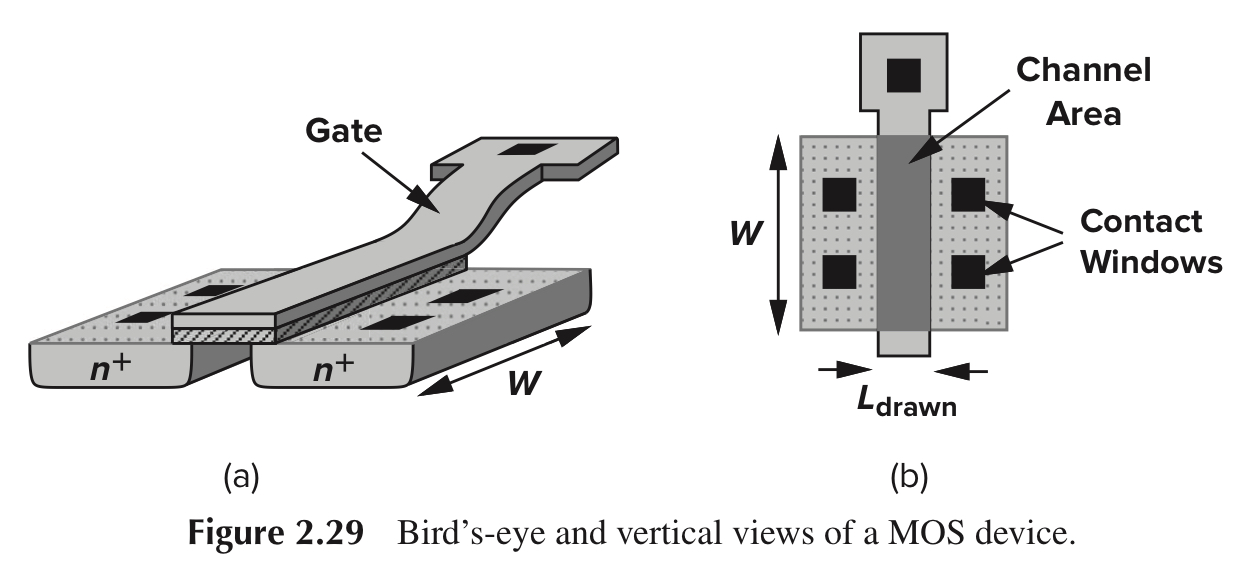

Figure 2.29의 두 그림은 각각 MOSFET의 "bird-eye's view"와 top view입니다.

Gate polysilicon과 source, drain terminal는 각각 metal(aluminum) wire에 연결되어야 합니다.

Metal wire는 resistance와 capacitance가 낮은 interconnect로 작용합니다.

이를 위해, 하나 이상의 "contact window"가 각 구역에 비어 있어, metal이 그 공간을 채워서 윗층의 metal wire과 연결합니다.

Gate poly는 channel area를 넘도록 길게 만드는데, 이는 transistor "edge"를 확실하게 구분하기 위해서입니다.

Source와 drain junction은 성능에 중요한 역할을 합니다.

Source와 drain junction의 capacitance가 크면 회로의 usage frequency와 switching 속도가 느려집니다.

따라서 S와 D의 capacitance를 최소화해야 하며, 그러기 위해서는 junction의 총 면적이 최소화되어야 합니다.

Capacitance의 공식이 아래와 같기 때문입니다.

Figure 2.29를 보면, S와 D junction의 한 모서리는 길이가 W입니다.

다른 한 모서리의 길이는 contact window를 뚫을 수 있을 만큼, 또 공정의 design rule을 만족하도록 충분히 긴 값이어야 합니다.

MOSFET Layout 예시

Figure 2.30(a) 회로의 layout을 그려 봅시다.

M1과 M2는 node C를 공유하고, M2와 M3는 node N을 공유하므로, layout은 Figure 2.30(b)와 같은 구조가 되어야 합니다.

나머지 연결들을 마치면 Figure 2.30(c)와 같은 layout이 그려집니다.