참고: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second Edition

Chapter 2 - Basic MOS Device Physics (pg.31~34)

2.4. MOS Device Models

2.4.3. MOS Small-Signal Model

Large-Signal Model과 Small-Signal Model

Triode, saturation region에서의 Id 공식인 Eq.(2.8)과 Eq.(2.9)에 설명된 quadratic characteristic과, 이전에 유도된 voltage-dependent capacitance는 MOSFET의 large-signal 모델을 형성합니다.

Large-signal model은 신호가 bias point를 심각하게 방해하는 회로나, 특히 nonlinear effect가 문제일 경우 필수적입니다.

반면, bias condition의 변화가 적을 경우, 계산을 간소화하기 위해 "small-signal" model을 사용하곤 합니다.

Small-signal model은 large-signal model의 operating point 근처에서 근사화한 것입니다.

많은 아날로그 회로에서 MOSFET이 saturation region에서 bias되기 때문에, saturation region에서 해당 small-signal model을 도출합니다.

스위치로 동착하는 transistor의 경우, Eq.(2.11)로 주어진 linear resistor와 device capacitance가 대략적인 small-signal 등가로 사용됩니다.

Small-Signal Model 도출 방법

우리는 하나의 bias parameter에 작은 증분(increment)을 가하고, 다른 bias parameter에서 발생하는 증분을 계산하여 small-signal model을 도출합니다.

구체적으로,

(1) Device의 terminal에 bias voltage를 가하고,

(2) 두 terminal 간 전위 차이를 증가시키는 동안 다른 terminal 전압은 일정하게 유지하며,

(3) 모든 terminal 전류의 변화를 측정합니다.

두 terminal 간 전압을 ΔV만큼 변화시키고, 일부 branch에서 전류 변화 ΔI를 측정하면, 그 효과를 voltage-dependent current source로 모델링할 수 있습니다.

Basic Small-Signal Model

ΔV = Vgs라는 small-signal 값을 변화로 적용해 봅시다.

이에 따라 Id는 gmVgs만큼 변하고, drain과 source terminal 사이의 voltage-dependent current source로 모델링됩니다.

이를 적용한 Figure 2.37(a)는 기본적인 MOS small-signal model입니다.

Gate 전류는 매우 작아 변화도 무시 가능하므로, small-signal model에서 다루지 않습니다.

Channel-Length Modulation을 반영한 Basic Small-Signal Model

이번에는 channel-length modulation도 고려해 봅시다.

Channel-length modulation 때문에, Id는 Vds에 의해서도 변하게 됩니다.

(Channel-length modulation에 대한 설명은 아래 링크에 있습니다.)

2024.10.06 - [반도체 소자] - [Razavi][Ch2] MOSFET Second-Order Effects(2) - Channel Length Modulation

[Razavi][Ch2] MOSFET Second-Order Effects(2) - Channel Length Modulation

출처: Behzad Razavi, Design of Analog CMOS Integrated Circuits, Second EditionChapter 2 - Basic MOS Device Physics (pg.23~24)2.3. Second-Order Effects이 단원 전까지는 MOS 구조를 쉽게 이해하기 위해, 실제 아날로그 회로와는 맞

soobdal.tistory.com

이 효과는 voltage-dependent current source로 모델링됩니다. (Figure 2.37(b))

그런데 전류값이 그 양단의 전압에 의존하는 current source는 linear resistor와 같다고 할 수 있습니다. (Figure 2.37(c))

따라서, channel-length modulation의 효과는 drain과 source 사이의 저항 ro로 나타내며, ro의 값은 아래와 같습니다.

여기서 λVDS << 1이라 가정합니다.

이 ro를 output resistance라 하며, 이는 많은 아날로그 회로의 성능에 영향을 미칩니다.

한 예로, ro는 대부분의 amplifier의 maximum voltage gain을 제한합니다.

Body effect를 반영한 Basic Small-Signal Model

이제 body effect도 고려해볼까요?

Body effect는 bulk potential이 Vth에 영향을 미쳐 gate-source overdrive (Vgs - Vth)도 바꾼다는 것이었습니다.

다른 terminal들의 전압이 일정할 때, Id는 bulk 전압에 대한 함수입니다. (교재 Example 2.3 참고) (??)

D와 S를 연결하는 current source로 이 의존성을 표현할 수 있습니다. (Figure 2.37(d))

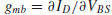

current source의 값을 gmbVb라 하고, gmb의 값은 아래와 같습니다.

Saturation region에서, gmb는 아래와 같이 나타낼 수 있습니다.

η의 값은 보통 약 0.25입니다.

gmVgs와 gmbVbs가 같은 polarity(전류 방향)를 갖는다는 점 짚고 넘어가겠습니다.

Gate voltage를 높이는 것이 bulk voltage를 높이는 것과 같은 효과를 갖는다는 뜻이죠.

대부분의 low-frequency small-signal analysis에 Figure 2.37(d)의 모델이 적합합니다.

Layout 변화를 통한 Terminal 저항 최소화

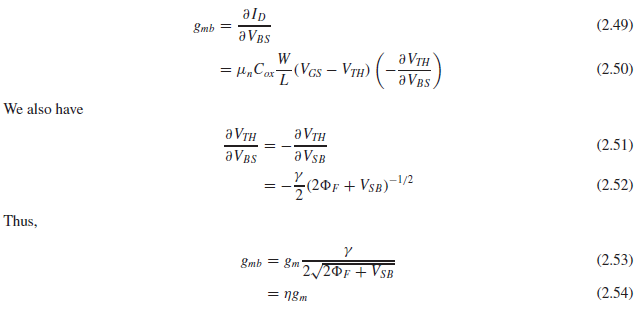

실제 설계에서는, MOSFET의 각 terminal은 재료(및 contact)의 resistivity로 인해 유한한 ohmic resistance를 나타내지만, 적절한 layout을 통해 이러한 저항을 최소화할 수 있습니다.

예를 들어, Figure 2.38의 두 구조를 보면, folding을 통해 gate resistance를 1/4배로 줄일 수 있다는 것을 알 수 있습니다.

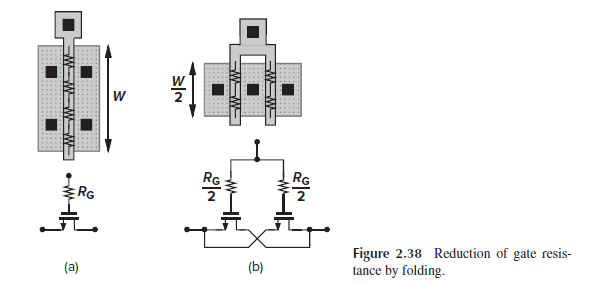

Complete Small-Signal Model

아래 그림은 device capacitance까지 포함한 complete small-signal model입니다.

회로를 분석하는 첫 단계에서는 아래 모델보다는 간단한 모델을 사용하여, 회로에 대한 직관을 키워야 합니다.

PMOS Small-Signal Model

결론적으로 PMOS와 NMOS의 small-signal model에는 차이가 없습니다.

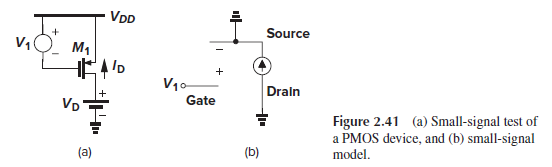

Figure 2.41(a)의 회로를 봅시다.

Saturation에 있는 M1에서 V1 값을 조금 변화시켰을 때의 Id의 변화를 볼 겁니다.

(PMOS에서 전류는 S→D 방향으로 흐르지만, NMOS와 전류 방향 표기를 통일하기 위해 Id를 D→S 방향으로 설정한 듯합니다.)

V1이 더 큰 양수가 되면(more positive), Vgs는 더욱 작은 음수가 됩니다(more negative).

그러면 PMOS가 더 큰 overdrive(Vsg - Vth)를 갖게 되어, 전류값 |Id|가 더 커집니다.

Id가 더 작은 음수가 된다는 말이죠.

즉, ΔVgs가 음수라면 ΔId 역시 음수입니다.

반대로, ΔVgs가 양수라면 ΔId 역시 양수가 되는데, 이는 NMOS의 경우와 동일합니다.

따라서 PMOS NMOS의 small-signal model에 차이가 없다는 겁니다.

우리는 PMOS device를 그릴 때 source가 위에, drain이 아래로 가게 그립니다.

PMOS의 source가 drain보다 더 positive한 전압을 가지기 때문입니다.

Figure 2.41(b)를 보면 volgate dependent current source가 위쪽을 향하고 있는데, 이 때문에 PMOS와 NMOS의 small-signal model이 다르다고 착각하시면 안 됩니다.

위아래를 바꾸면 같은 회로이기 때문입니다.

'CMOS IC Design' 카테고리의 다른 글

| (개요) Single-Stage Amplifiers [Razavi][Ch3] (0) | 2024.10.29 |

|---|---|

| FinFETs, MOSCAP [Razavi][Ch2] (0) | 2024.10.29 |

| MOSFET Parasitic Capacitances(Device Capacitances) [Razavi][Ch2] (1) | 2024.10.06 |

| MOSFET Device Layout(Contact Window, Metal Wire, Design Rule) [Razavi][Ch2] (1) | 2024.10.06 |

| MOSFET Second-Order Effects(4) - Voltage Limatations, Punch-Through [Razavi][Ch2] (1) | 2024.10.06 |